#### AVERTISSEMENT

Ce document est le fruit d'un long travail approuvé par le jury de soutenance et mis à disposition de l'ensemble de la communauté universitaire élargie.

Il est soumis à la propriété intellectuelle de l'auteur. Ceci implique une obligation de citation et de référencement lors de l'utilisation de ce document.

D'autre part, toute contrefaçon, plagiat, reproduction illicite encourt une poursuite pénale.

Contact : ddoc-theses-contact@univ-lorraine.fr

#### LIENS

Code de la Propriété Intellectuelle. articles L 122. 4 Code de la Propriété Intellectuelle. articles L 335.2- L 335.10 <u>http://www.cfcopies.com/V2/leg/leg\_droi.php</u> <u>http://www.culture.gouv.fr/culture/infos-pratiques/droits/protection.htm</u>

## THÈSE

En vue de l'obtention du

### Doctorat de l'Université de Lorraine

#### Mention : Génie Électrique

par

#### Davide DELL'ISOLA

# « Optimization of DC/DC converters for embedded systems including dynamic constraints»

Membres du jury :

| Président                             |                                                    |

|---------------------------------------|----------------------------------------------------|

| Prof. Mohamed MACHMOUM                | Université de Nantes, IREENA                       |

| Rapporteurs                           |                                                    |

| Prof. Corinne ALONSO                  | Université de Toulouse-III-Paul-<br>Sabatier, LAAS |

| Prof. Eric MONMASSON                  | Université de Cergy-Pontoise,<br>SATIE             |

| Examinateurs                          |                                                    |

| Prof. Farid MEIBODY-TABAR (Directeur) | Université de Lorraine, LEMTA                      |

| Dr. Matthieu URBAIN (Co-Directeur)    | Université de Lorraine, LEMTA                      |

| Invité                                |                                                    |

| Prof. Serge PIERFEDERICI              | Université de Lorraine, LEMTA                      |

## Acknowledgments

This thesis work was carried out in the GREEN (Groupe de Recherche en Energie Electrique de Nancy) laboratory of Nancy, at the University of Lorraine, under the direction of Farid Meibody-Tabar, Professor at LEMTA laboratory, University of Lorraine, and Matthieu Urbain, Senior Lecturer at LEMTA.

I would like to thank Mr Bernard Davat, former director of the GREEN when I started my thesis, for having welcomed me in the laboratory, and Mr. Noureddine Takorabet as well, his successor as director of the GREEN laboratory, for his help, availability and valuable administration.

I would also like to express my sincere gratitude to Mrs. Corinne Alonso, Professor at LAAS laboratory, University of Toulouse-III-Paul-Sabatier, and Mr. Eric Monmasson, Professor at SATIE laboratory, University of Cergy-Pontoise for being interested in my work and for agreeing to report my thesis. My sincere thanks also go to Mr. Mohamed Machmoum, Professor a IREENA, University of Nantes, for taking part in the jury of my thesis defence as the President of the Jury.

I would like to thank my thesis supervisors, Mr Farid Meibody-Tabar and Mr Matthieu Urbain, for their involvement throughout these years. I could not have wished for better supervision. Their knowledge and support, and a laugh now and then, allowed me to progress professionally and achieve the results described in this manuscript.

I would like to thank Mr. Serge Pierfederici, Professor at LEMTA laboratory, who first introduced me in the GREEN laboratory during my Master project, through an Erasmus Placement program. His invaluable help and experience have walked me through the whole course of my PhD experience.

Special thanks go to the valuable people I worked with in these years, such as Thierry, Ignace, Jean-Philippe and Roghayeh.

I would like to thank the GREEN staff, starting from Sylvie and Latifa, for their irreplaceable help and kindness. I am thinking of course to the technical staff as well, to Fabrice, Fadi, Sylvie, Isabelle and Matthieu (from LEMTA). Without their experience and savoir-faire, I could not have achieved the following results.

These years definitely would not have been the same without my colleagues. During my PhD, many people have come and gone, but none of them that are not worth remembering. I will start of course from the old guard. I have to thank Ivano, the first person I met who welcomed me to Nancy. He introduced me to the French world and helped me to overcome my prejudices against the redheaded people. Special thanks go to Bomber, my "creatura", my most relevant and accomplished project. Without him, I would not even be able to eat the cancoillotte properly.

Thanks to the "anciennes", the reunion colleagues. How not to remember Hugues, Marc and his skill with darts, the "bon copain" Cyril, and Geoffrey, with his strong aptitude to accept the defeat. Special thanks go to Najla and Hassan "la touche", who taught me the finest words in Lebanese.

I want to thank the new generation as well. I am thinking about Thibaud, who probably will not even remember my name when I will leave Nancy, and my voluminous friends Abdou and Francois. I would like to express a sincere gratitude for the contribution of Pang. Of course, I cannot forget to thank Saeid, Dominique, Baptiste, Hamid, JB, Thomas, Quentin, Max, and Peyman.

I warmly thank my friends Tommaso and Daniele, with whom I have shared unforgettable experiences, which could span from moments of enlightened culture to levels of profound ruthlessness.

My most sincere gratitude and love go to my Isidora, who has helped me grow for most of my life and has been close to me in all the most important moments, in ways that even she does not fully understand.

Finally, my heartfelt gratitude goes without a doubt to my family, my brothers and my parents. Without them, their support, nothing of this could have happened. Besides that, I thank them in particular for always reminding me that, no matter where my choices will take me, I will always have a home.

## Résumé en Français

En raison de la pénurie progressive de combustibles fossiles et de l'urgence environnementale, des accords internationaux ont été conclus pour contenir la croissance de la température moyenne mondiale à long terme. Les directives introduites visent à faire converger les flux financiers vers un développement économique respectueux de l'environnement et à orienter les efforts de la communauté industrielle vers une réduction des émissions des gaz à effet de serre, en particulier dans le secteur des transports, dont le taux d'augmentation de la consommation d'énergie (ainsi que des émissions de gaz à effet de serre) est le plus élevé au cours des dernières décennies.

L'industrie aéronautique et automobile privilégie des solutions plus efficaces et plus autonomes, ce qui a conduit à une électrification considérable des systèmes de conversion d'énergie à bord. Le marché des véhicules électriques ou hybrides électriques est en croissance constante. L'échange d'énergie entre les unités de stockage, le système d'actionnement du groupe motopropulseur, le moteur/générateur à combustion interne et les nombreuses charges est assuré par un réseau DC, et chaque source/charge nécessite l'insertion d'un convertisseur d'interface spécifique. En même temps, dans le réseau électrique du réseau d'avions modernes (More Electrical Aircraft, MEA), plusieurs unités mécaniques ont été remplacées par des homologues électriques, au profit de l'efficacité et du poids du système global.

Pour alimenter les différentes charges de puissance à bord, les unités d'électronique de puissance sont constituées de convertisseurs de puissance à découpage, dont le fonctionnement s'effectue par la commutation des transistors à semi-conducteurs. L'évolution des convertisseurs de puissance s'améliore en même temps que les progrès technologiques des dispositifs à semi-conducteurs. Comme expliqué dans le premier chapitre, les dispositifs à base de silicium domine le marché depuis les trois dernières décennies. Pour des applications d'une centaine de kW, le transistor bipolaire IGBT a été le dispositif le plus utilisé en raison de ses calibres de courant et de tension élevés (par rapport aux dispositifs unipolaires MOSFET). Néanmoins, en raison de la nature bipolaire de la structure IGBT, la fréquence de commutation du convertisseur de puissance, lorsque ce dispositif est utilisé, est limitée par les temps de commutation du dispositif. D'autre part, la recherche sur les matériaux semi-conducteurs à grand gap (WBG, wide band-gap) a conduit à l'introduction de nouveaux dispositifs à hautes performances suffisamment matures pour être proposés sur le marché. Les caractéristiques des matériaux WBG comme le carbure de silicium ou le nitrure de gallium permettent de construire des dispositifs unipolaires, comme le transistor à effet de champ métal-oxyde-semiconductor (MOSFET), avec les mêmes calibres de courant et de tension des IGBT du commerce, une température de fonctionnement plus élevée, des pertes de conduction plus faibles et des temps de commutation plus rapides. La possibilité d'augmenter sensiblement la fréquence de commutation tout en maintenant les pertes de puissance à un faible niveau permet d'améliorer globalement le système de conversion en termes d'efficacité et de taille des éléments passifs et du système de refroidissement. La diffusion de ces dispositifs offre des possibilités évidentes pour considérablement améliorer les systèmes électroniques de puissance de conversion.

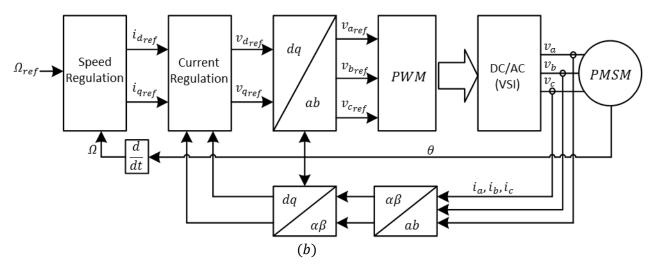

Compte tenu de ces critères, cette étude a pour objectif le développement d'une procédure de dimensionnement optimale d'un convertisseur dans un réseau embarqué. Le convertisseur a été conçu spécifiquement pour une structure d'alimentation d'un actionneur. Afin d'assurer la bonne interaction entre la charge (onduleur DC/AC et moteur) et le micro-réseau de bord, le dimensionnement doit prendre en compte la stabilité et le comportement dynamique du convertisseur lors d'une éventuelle variation du point de fonctionnement, donc sa stratégie de contrôle.

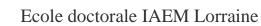

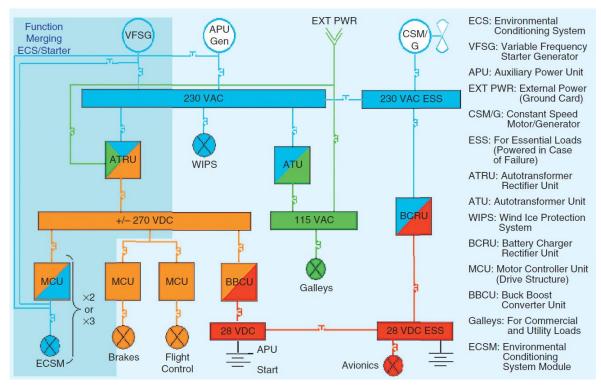

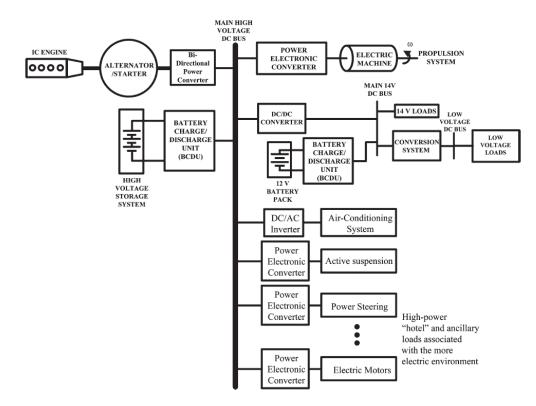

Le réseau de distribution d'énergie électrique à bord d'un avion moderne est composé d'un bus de tension alternative et d'un bus de tension continue alimenté par le réseau alternatif par l'intermédiaire d'unités de redressement, comme montré en Figure 1.

Figure 1 Exemple de micro-réseau DC embarqué dans un MEA.

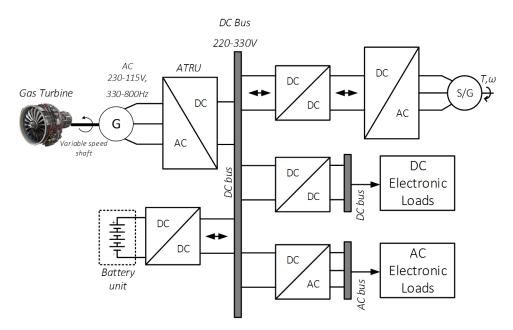

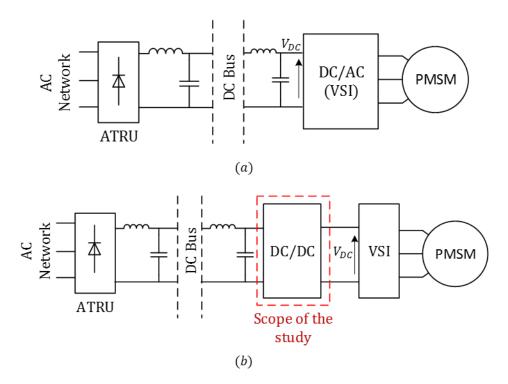

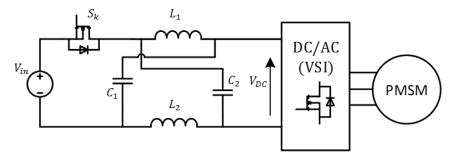

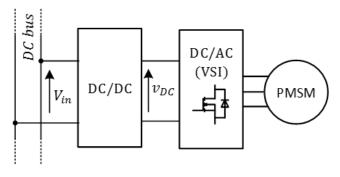

Dans le cas spécifique des avions plus électriques, la variation la plus remarquable est l'absence de l'unité de boîte de vitesse (internal drive generator, IDG) pour la génération de l'énergie électrique AC à fréquence et à amplitude de tension fixes à partir de la turbine à gaz. L'amplitude et la fréquence de la tension alternative générée par la turbine sont variables, ce qui entraîne une modification de la tension du bus continu générée par un redresseur. Ensuite, les charges électriques et mécaniques sont alimentées par des convertisseurs DC/DC ou DC/AC (selon la charge) connectés au bus DC de distribution pour assurer une tension stable. Dans ce contexte, l'efficacité, la taille et le niveau d'intégration de la conversion électronique de puissance constituent les principales contraintes. Pour une application de groupe motopropulseur embarqué, l'étage d'électronique de puissance est souvent composé d'un simple onduleur connecté au bus DC par un filtre d'entrée (Figure 2(a)).

*Figure 2 Chaîne de conversion classique (a) pour l'alimentation d'un moteur et avec un convertisseur DC/DC entre le bus DC et l'onduleur (b).*

Comme expliqué dans le chapitre 2, une alternative intéressante consiste à insérer un convertisseur DC/DC entre le filtre et l'onduleur (Figure 2(b)). Cette solution permet d'immuniser l'onduleur contre les perturbations de tension sur le bus DC, en particulier dans le cas d'un réseau électrique dans un avion moderne. En effet, si la chaîne d'entraînement est uniquement composée de l'onduleur et du filtre d'entrée, les enroulements du stator du moteur doivent être conçus pour fonctionner de manière à assurer la contrôlabilité du couple moteur pour toute la plage de variation de la valeur de tension du bus DC, ce qui entraîne une augmentation des pertes de puissance dans l'onduleur et un surdimensionnement conséquent de ses composants actifs et de son unité de refroidissement. Le convertisseur DC/DC offre la possibilité d'optimiser l'efficacité de la chaîne d'actionnement dans toute la gamme de vitesse de fonctionnement.

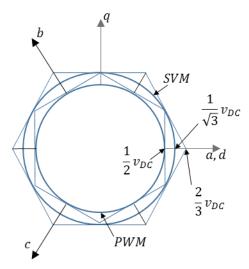

En outre, un modulation d'amplitude (pulse amplitude modulation, PAM) pour la génération de signaux de commande peut être mis en œuvre, ce qui permet de réduire le nombre de commutations des dispositifs d'inversion pendant la période mécanique de la charge AC, dans ce cas un moteur synchrone à aimants permanents (PMSM), et diminue la distorsion de l'ondulation du courant dans les enroulements du moteur, ce qui est nuisible pour le moteur lui-même et pour le contrôle du couple. Les architectures de convertisseurs DC/DC les plus classiques ont été présentées pour la tâche envisagée. Selon le profil de la mission, il pourrait être plus avantageux d'utiliser un convertisseur élévateur pour une application à grande vitesse, ou un convertisseur élévateur/abaisseur pour une application à large gamme de vitesse.

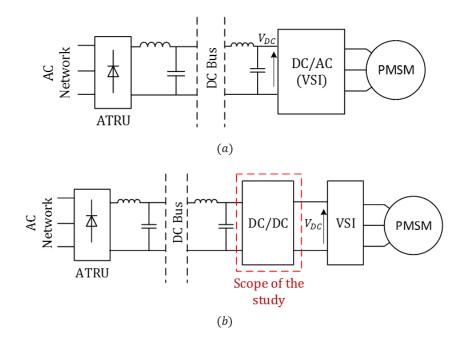

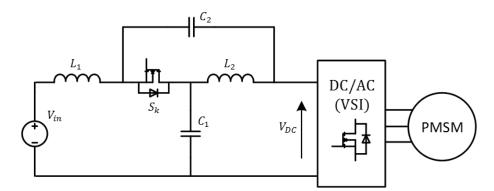

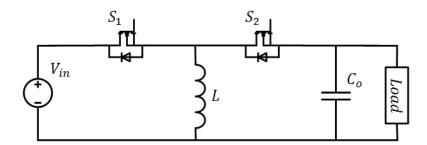

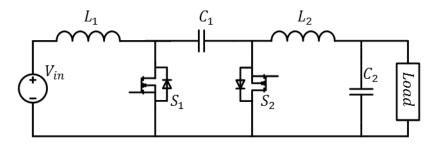

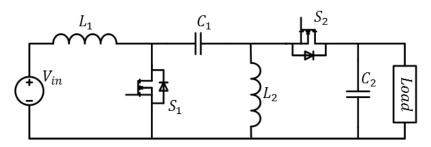

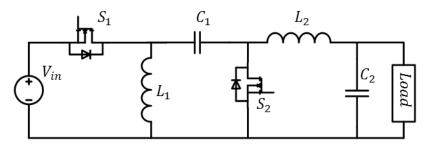

Le chapitre 2 présente les topologies de convertisseurs DC/DC les plus courantes pour ce type d'application. Pour le cas spécifique de la chaine d'entrainement d'un actionneur démarreur (starter), une topologie originale de type "step-up/down" est présentée et analysée.

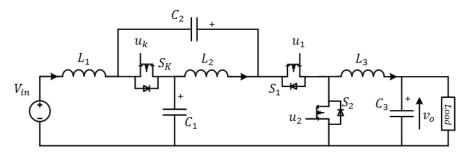

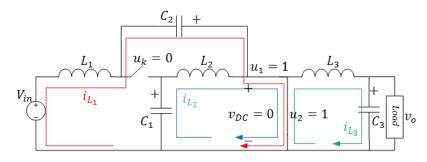

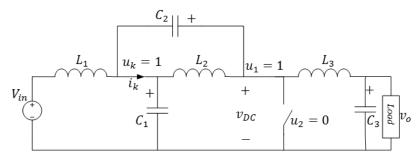

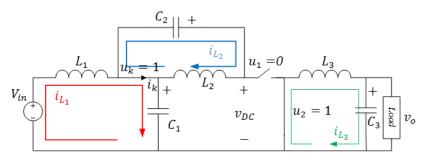

Figure 3 Topologie proposée de convertisseur DC/DC Quasi Z-Source step up/down.

La topologie proposée est composée d'un convertisseur Quasi Z-Source et un convertisseur Buck (QZSBC), comme montré en Figure 3. Le QZSBC proposé est une topologie intéressante lorsque la conversion de tension est requise pour un mode principalement abaisseur. En effet, l'application du cycle de fonctionnement d'un actionneur starter nécessite une faible vitesse du moteur pour la plupart du temps, donc la partie de conversion DC/DC doit fournir principalement une faible tension de sortie. Pendant une brève partie de toute la période du cycle, le convertisseur fournit une tension de sortie élevée afin de permettre à l'actionneur d'atteindre des vitesses plus élevées. De plus, la version à inductances couplées de la topologie permet de supprimer l'ondulation du courant d'entrée à la fréquence de commutation, ce qui apporte un grand gain de masse sur la conception du filtre d'entrée. Un prototype de convertisseur de 3 kW a été réalisé et les résultats expérimentaux montrent sa faisabilité.

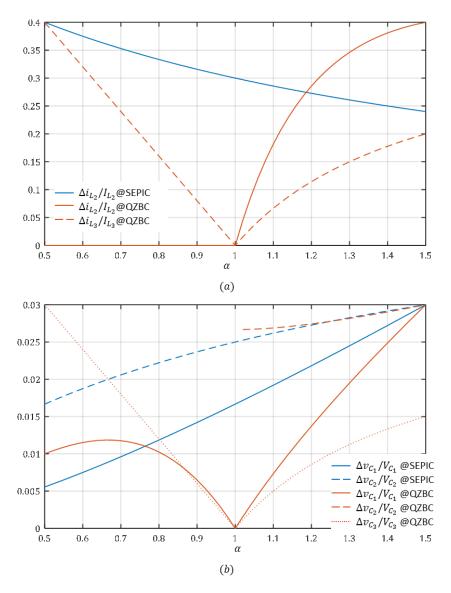

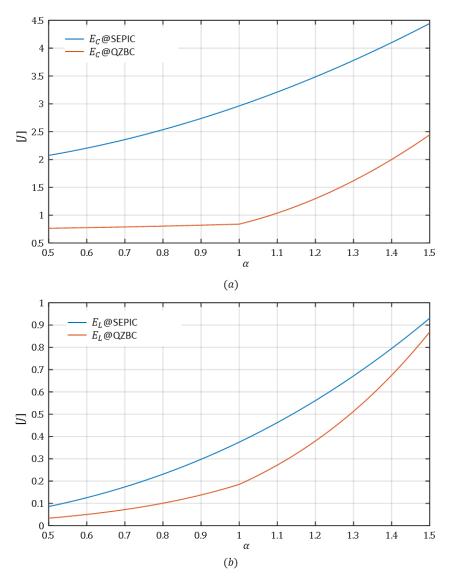

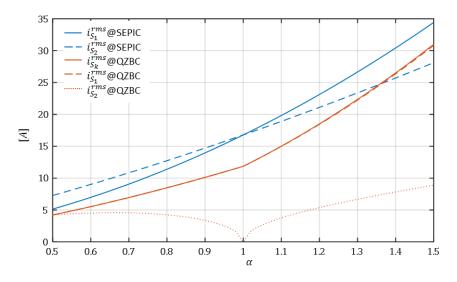

Le convertisseur QZSBC a été comparé à un convertisseur SEPIC classique. Cette topologie a été choisie en raison de la caractéristique commune concernant le courant d'entrée continu et la possibilité de supprimer l'ondulation du courant d'entrée. La comparaison a été menée afin de montrer les contraintes de tension et de courant dans les composants actifs et passifs des convertisseurs pour une gamme donnée de gain de tension. La quantité d'énergie magnétique et électrostatique stockée par les composants passifs montre que la QZSBC stocke moins d'énergie, ce qui signifie que, en raison de la relation entre l'énergie stockée et la taille des composants passifs, la QZSBC nécessite des condensateurs et des inductances plus petits pour la plage de fonctionnement considérée. En outre, l'analyse des

courants efficaces et des tensions inverses sur les dispositifs à commutation dure suggère que les pertes de puissance dans le convertisseur proposé sont plus faibles pour la plage de fonctionnement en mode abaisseur et comparables pour le mode élévateur. Par conséquent, l'efficacité du QZSBC mesurée sur un cycle de mission entier sera supérieure à celle du SEPIC, ce qui signifie que le convertisseur a globalement de meilleures performances dans l'application mentionnée.

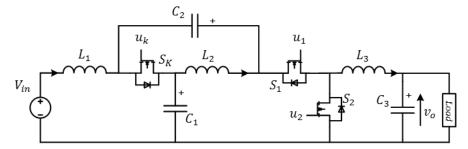

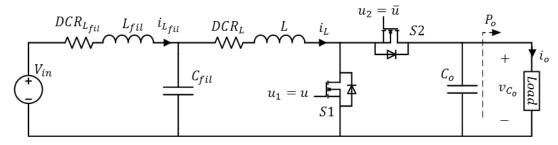

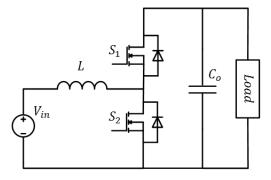

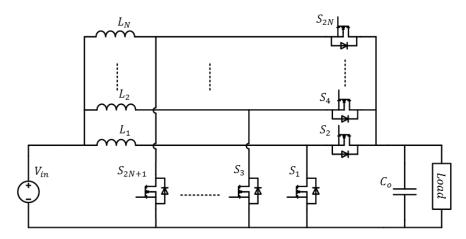

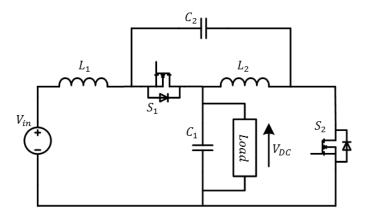

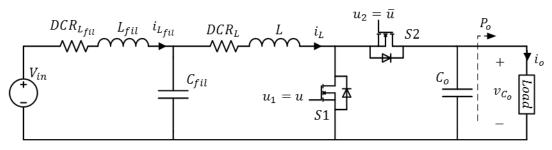

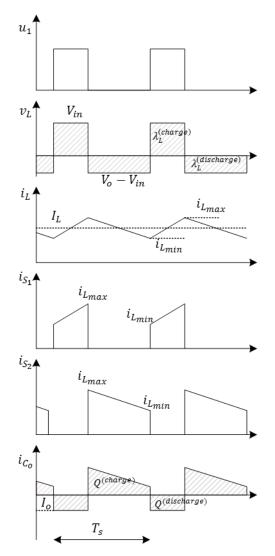

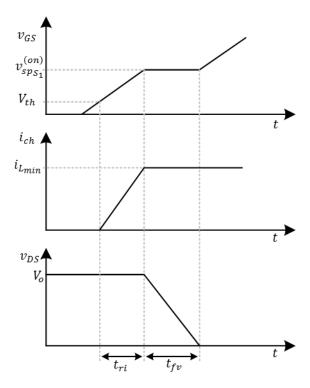

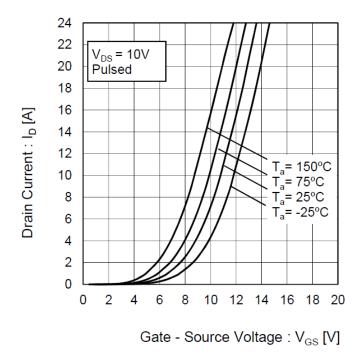

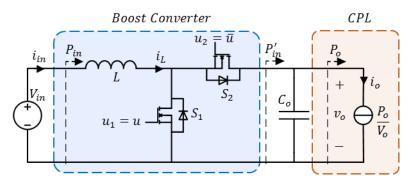

Les principales exigences pour l'application d'entraînement moteur décrite sont clairement la compacité et l'efficacité. Cependant, le problème de conception d'un convertisseur DC/DC n'est pas une tâche triviale, surtout lorsqu'il s'agit d'optimiser des performances multiples. Plusieurs variables relatives à chaque composant sont impliquées, qui appartiennent à différents domaines d'ingénierie (électrique, magnétique, thermique...). De plus, la plupart des variables sont liées les unes aux autres. Pour atteindre différents objectifs (efficacité et compacité), le concepteur doit avoir une connaissance approfondie de l'influence de chaque variable de conception, afin de faire les compromis appropriés et de respecter les contraintes de faisabilité et d'application. Il convient de noter que les paramètres de conception sont par ailleurs restreints à la disponibilité des composants sur le marché. Dans le chapitre 3, le problème de conception de la partie de puissance d'un convertisseur Boost (Figure 3) et de son filtre d'entrée est décrit pour chaque élément.

Figure 4 Convertisseur Boost DC/DC et filtre d'entrée différentiel.

Les modèles analytiques utilisés, les variables et les paramètres relatifs sont présentés afin de comprendre les compromis impliqués dans la conception de l'étage de puissance du convertisseur. Dans ce chapitre, les principaux éléments d'un convertisseur ont été abordés et leur rôle et leur impact sur les performances du convertisseur ont été analysés. Les paramètres de conception des composants et les modèles de performances présentés seront précieux pour le chapitre 5 afin de réaliser une optimisation globale du convertisseur.

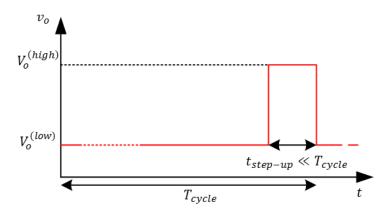

Un aspect souvent pris en compte est le comportement dynamique du convertisseur, tel que la réponse à une variation du point de fonctionnement ou à une perturbation, malheureusement il est fréquemment envisagé après la conception de la partie puissance du convertisseur. Dans l'application considérée du groupe motopropulseur, si le moteur doit fournir un échelon de couple, le courant requis par le convertisseur augmente fortement en raison du contrôle rapide des courants de phase du moteur. Un tel appel de puissance de charge pourrait provoquer une chute de la tension de sortie du convertisseur DC/DC, ce qui pourrait affecter la contrôlabilité des courants de phase. La réponse dynamique de la tension de sortie du convertisseur aux variations de la charge de puissance ne dépend pas exclusivement de la stratégie de contrôle et de ses paramètres, mais aussi des composants et des paramètres de l'étage de puissance, tels que les composants passifs et la fréquence de commutation. Comme présenté dans le chapitre 4 à travers les principes fondamentaux de la théorie des systèmes linéaires, les éléments passifs du convertisseur ont une forte influence sur le comportement dynamique du convertisseur, <del>puis</del> et sur la conception du contrôleur et la stabilité du système. De plus, en raison des limitations pratiques des régulateurs (bande passante finie, saturation des signaux de commande), l'excursion des courants/tensions des composants passifs ne peut être réduite en dessous d'un certain niveau. Les composants passifs doivent être spécifiquement conçus pour assurer la pleine conformité avec le cahier des charges et les contraintes sur l'excursion de courant et tension aux bornes d'entrée et de sortie du convertisseur lors des variations du point de fonctionnement prévue dans le cycle de la mission.

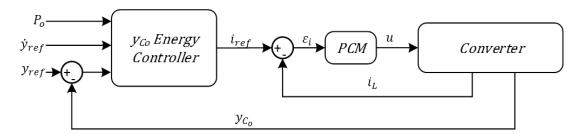

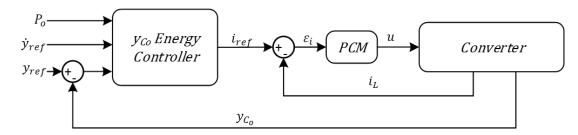

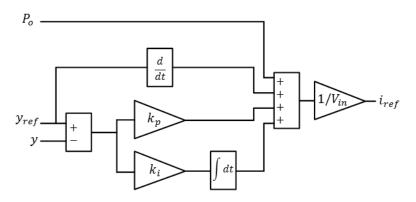

L'analyse dynamique a été menée pour le convertisseur Boost DC/DC, et le système a été caractérisé au moyen d'une modélisation des petits signaux. L'analyse de la fréquence des fonctions de transfert du convertisseur a montré des limitations dynamiques dues au zéro dans le demi-plan droit, commun à toutes les topologies dérivées du convertisseur Boost. Ce problème est un facteur limitant pour la stratégie de contrôle du convertisseur. Il a été démontré que le choix d'une stratégie de commande à boucle unique est inadapté à la gamme de valeurs des paramètres du circuit (fréquence de commutation, valeurs de capacité et d'inductance) habituellement considérés pour de telles applications. Une stratégie à deux boucles, comme dans le schéma de contrôle en Figure 5, est plus appropriée, elle permet également de contrôler le courant de l'inducteur et de contenir sa variation.

Figure 5 Schéma de contrôle à double boucle, avec régulation d''énergie.

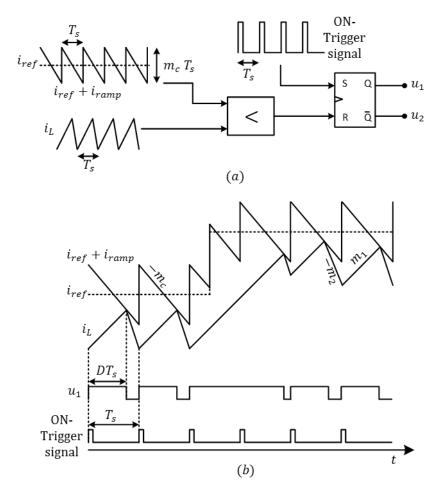

Quant à la boucle de courant interne, un régulateur de courant pic a été retenu en raison de sa robustesse, de sa rapidité et de son utilisation répandue dans ce type d'applications.

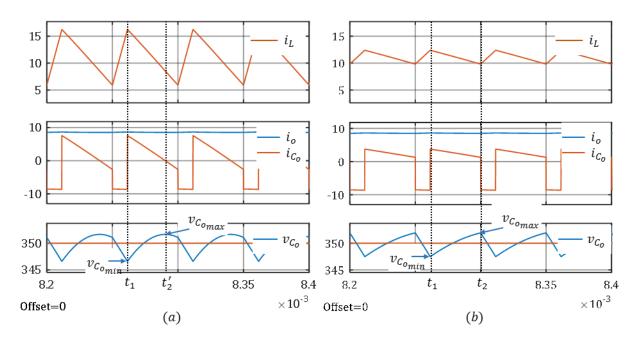

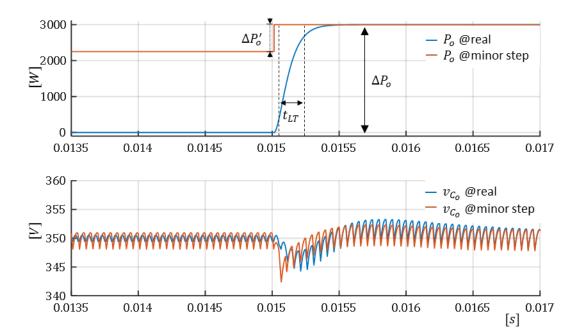

La tâche principale étant de contenir la variation de la tension de sortie lors d'une éventuelle variation de la puissance de sortie, une stratégie de contrôle se caractérisant par un meilleur rejet des perturbations de la charge de sortie a été proposée pour la boucle de contrôle externe. Ce régulateur contrôle l'énergie stockée dans la capacité de sortie, donc la tension de sortie indirectement.

Si le contrôleur assure une bonne immunité aux perturbations de la charge, le condensateur de sortie ne doit pas être surdimensionné pour contenir l'excursion de la tension de sortie. À cet égard, une méthode analytique de conception du condensateur de sortie a été proposée afin de maintenir la tension de sortie inférieure/supérieure du système contrôlé pendant les transitoires de puissance de charge dans les limites d'excursion de tension. La valeur minimale de la capacité obtenue dépendra des paramètres du point de fonctionnement, de la fréquence de commutation, de la valeur de l'inductance et des paramètres du contrôleur également.

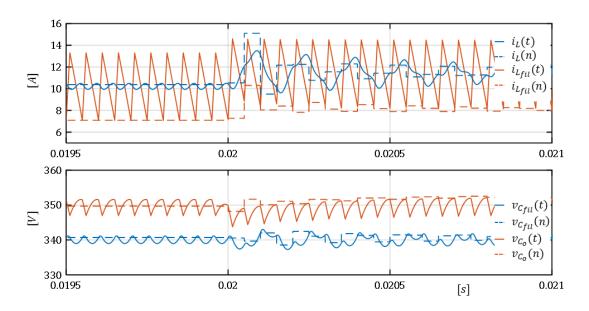

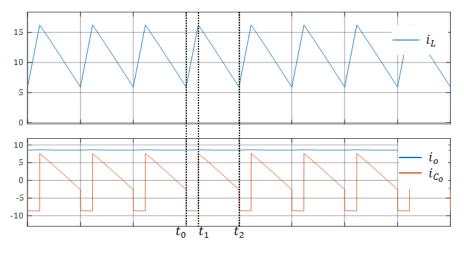

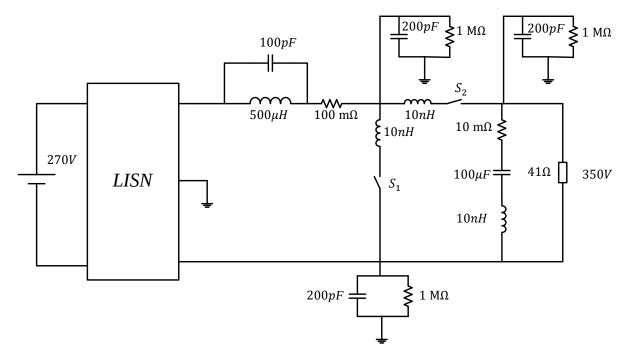

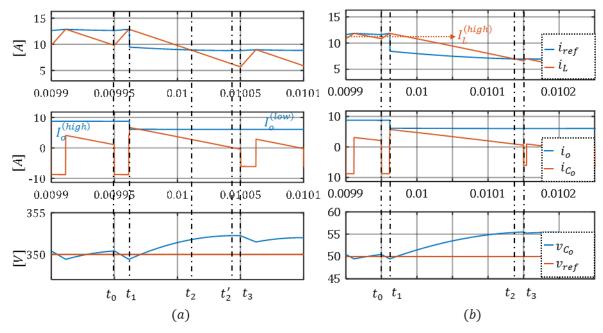

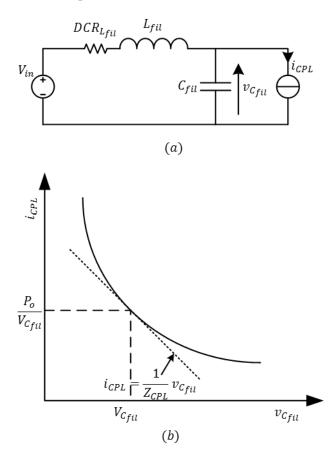

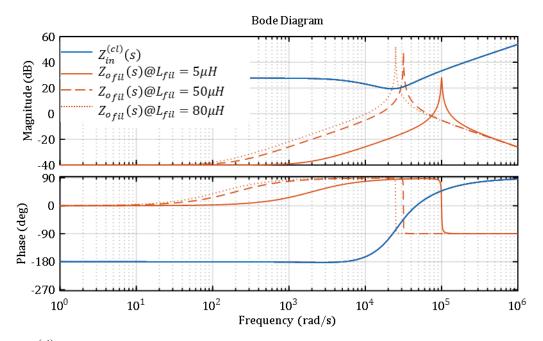

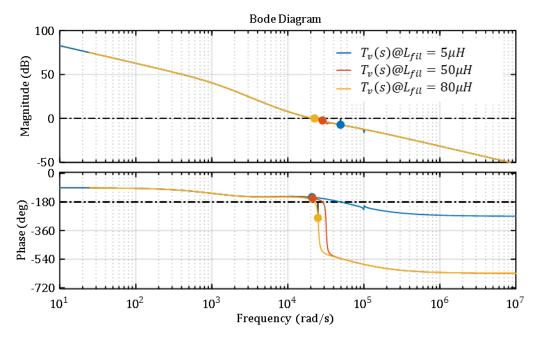

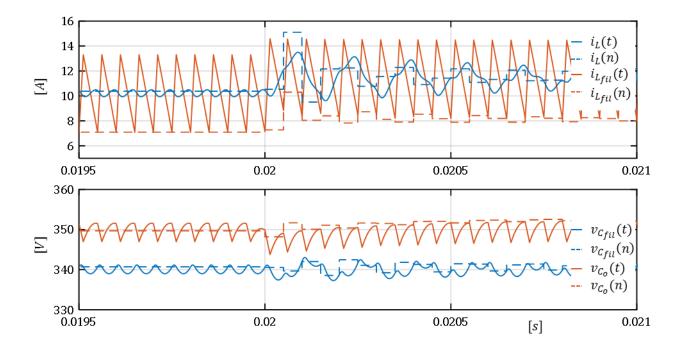

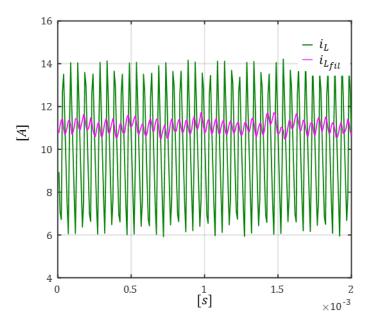

Dans la dernière section du chapitre 4, la question de la stabilité est abordée. En raison de la haute performance dynamique du régulateur de courant d'entrée du convertisseur, le comportement dynamique de l'ensemble de l'actionneur peut être considéré comme une charge à puissance constante avec impédance négative, ce qui pourrait conduire à des problèmes d'instabilité. L'interaction entre le système en boucle fermée et le filtre d'entrée a été analysée dans le domaine linéaire dans une première approche, en particulier en analysant l'impédance d'entrée du système en boucle fermée et l'impédance de sortie du filtre affecte les pôles du système global. Cette méthode, même si elle est largement utilisée, ne permet pas d'inclure les effets non linéaires dus au comportement de commutation du système réel. Pour cette raison, un outil plus fiable a été développé pour analyser la stabilité du système en régime permanent pour en déduire sa matrice dynamique (Jacobienne). L'évolution temporelle du système discret est cohérente avec celle du système à temps continu en simulation (Figure 6), ce qui prouve la fiabilité du système obtenu.

Figure 6 Comparaison entre la simulation à éléments réels et le modèle discret développé.

L'analyse des valeurs propres de la matrice permet de vérifier la stabilité du système composé par le filtre d'entrée LC, le convertisseur DC/DC et une charge de puissance constante. Cet outil est plus susceptible d'être inclus dans une routine d'optimisation, comme indiqué dans le chapitre 5.

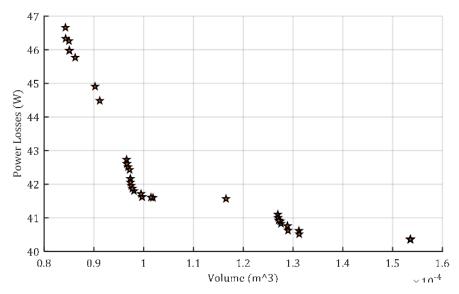

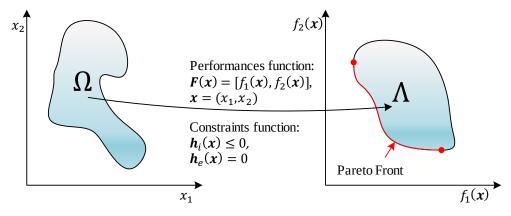

Alors que l'optimisation de la compacité et de l'efficacité du seul circuit électrique du convertisseur était une tâche non triviale, elle est encore plus compliquée si l'on tient compte du comportement dynamique, y compris la stratégie de contrôle et les paramètres respectifs. Afin d'aborder les nombreuses variables et paramètres impliqués dans le problème de l'optimisation (de la partie puissance et du contrôleur), un outil d'optimisation multi-objectifs a été développé dans le chapitre 5. Grâce à la procédure proposée, les solutions de dimensionnement les plus avantageux en termes d'efficacité et de compacité sont identifiées.

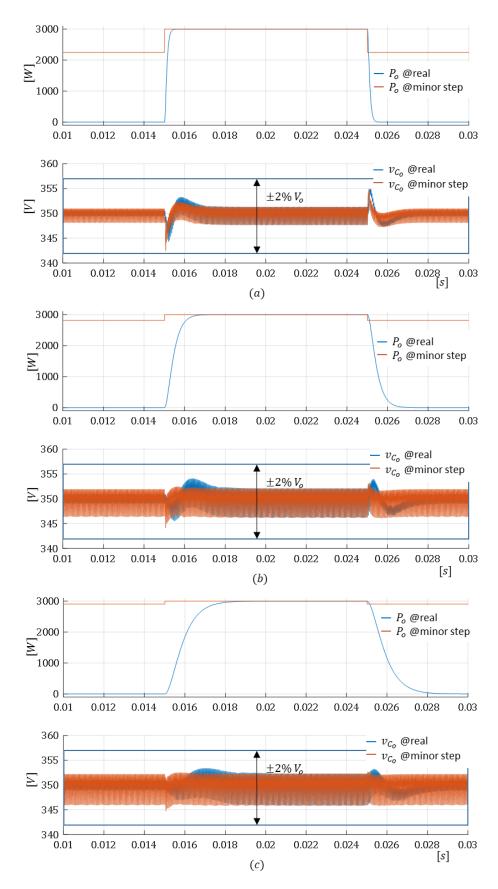

Outre le comportement en régime permanent, l'algorithme développé tient compte de la dynamique du convertisseur pendant la variation de la puissance de la charge. Cela signifie que l'évaluation des solutions implique la sélection simultanée des paramètres de l'étage de puissance et du régulateur, ce qui garantit une conception optimale capable de répondre aux spécifications tant en régime permanent qu'en régime transitoire. En outre, la stabilité du système composé du convertisseur, de la charge et du filtre d'entrée est également assurée.

Dans le chapitre 5, les limites des approches de conception traditionnelles pour les convertisseurs de puissance ont été discutées, en particulier lorsque l'optimisation de performances multiples est nécessaire. Les outils les plus utilisés pour la résolution d'un problème d'optimisation multi-objectifs dans le domaine de la conversion de puissance consistent en des algorithmes stochastiques, basés sur des procès évolutifs. En particulier, les principes fondamentaux d'un problème multi-objectifs ont été introduits et l'approche de résolution basée sur un algorithme génétique élitiste a été discutée. Plus précisément, un algorithme génétique non dominé a été utilisé (non-dominated sorting genethic algorithm, NSGA-II), ce qui garantit à la fois la convergence et la diversité des solutions de dimensionnement. Après une brève introduction de la structure et des principales étapes de la NSGA II, le problème de conception du système composé d'un convertisseur DC-DC boost de 3kW et du filtre d'entrée différentiel a été formulé afin de s'adapter à la procédure d'optimisation. Ainsi, l'objectifs et les fonctions de contraintes ont été définis selon les modèles des composants du convertisseur décrits dans le chapitre 3. Les variables de conception considérées ont été choisies de manière opportune en fonction du degré de liberté du problème et afin de tenir compte de la disponibilité commerciale des composants sur le marché. Les spécifications de conception comprennent la limite d'excursion de la tension de sortie à la fois en régime permanent et lors d'événements transitoires de la puissance de charge, et les exigences

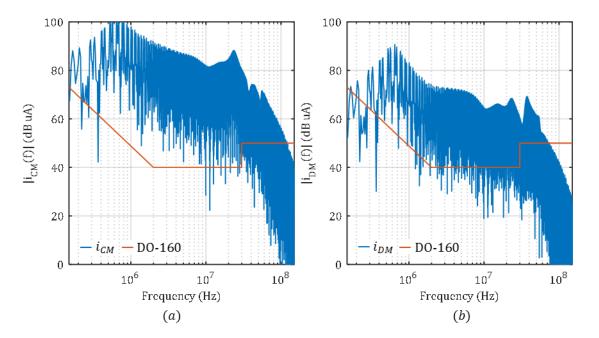

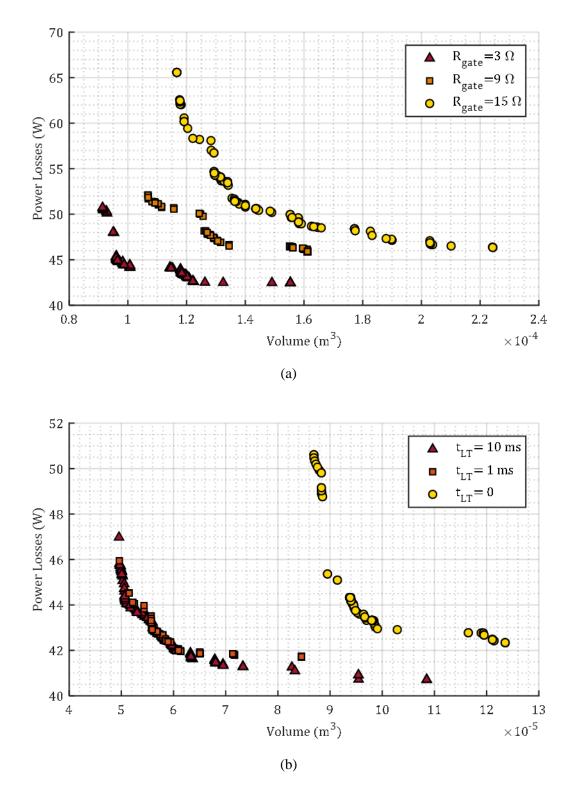

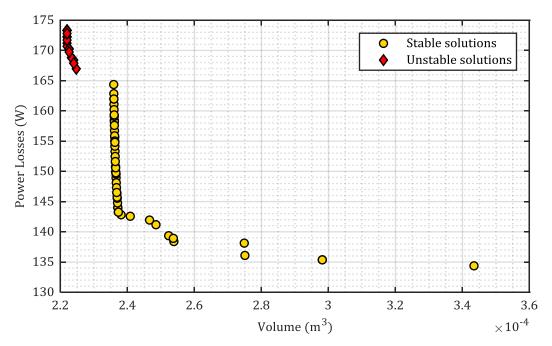

de la norme DO-160 à basse fréquence sur l'ondulation du courant d'entrée en régime permanent. Le convertisseur alimente un charge a puissance constante (constant power load, CPL), qui représente le cas le plus défavorable en termes de stabilité. Dans la littérature, les optimisations proposées pour les convertisseurs visent à développer des procédures de conception uniquement pour le mode de fonctionnement en régime permanent ; le comportement dynamique en cas de perturbations ou de variations du point de fonctionnement est souvent négligé dans la phase de dimensionnement. Dans la méthode proposée, puisque le convertisseur est conçu pour résister à d'éventuels transitoires de puissance de charge, la stratégie de contrôle et ses paramètres ont été inclus dans la routine d'optimisation. En outre, en raison de la présence du filtre LC d'entrée, l'algorithme d'optimisation inclut l'étude de la stabilité du système au moyen de cycles limites et écarte les solutions de conception instables. L'algorithme trouve les solutions de conception optimales, qui constituent le meilleur compromis entre le volume et les pertes de puissance, indiqué sur le Front Pareto en Figure 7.

Figure 7 Pareto Front obtenu de l'algorithme d'optimisation exécutée pour un convertisseur boost pour un point de fonctionnement  $V_{in} = 270V$ ,  $V_o = 350V$ ,  $P_o = 3kW$ .

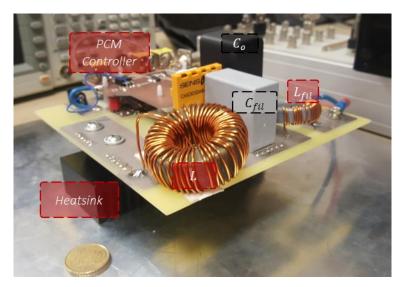

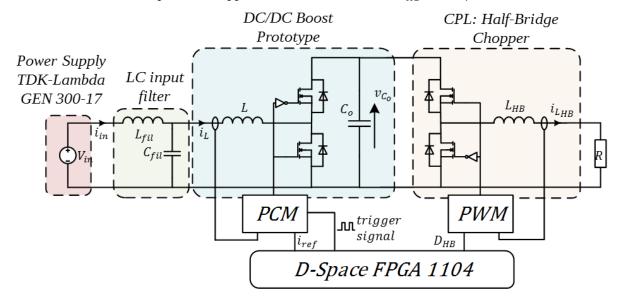

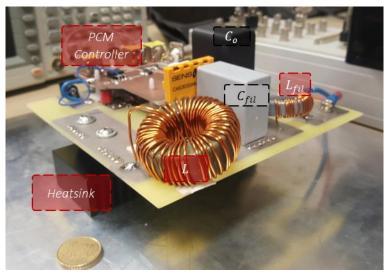

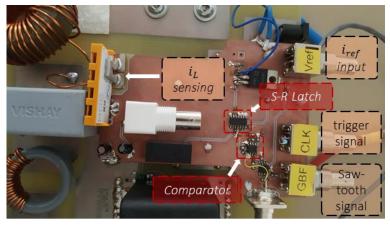

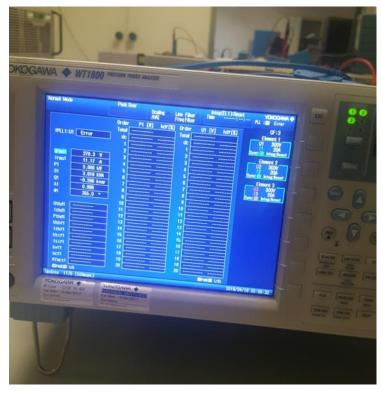

Les solutions obtenues ont été analysées afin de mettre en évidence les valeurs optimales des variables de dimensionnement et le compromis qui en résulte. Les fronts de Pareto obtenus par l'algorithme génétique montrent qu'il est possible d'augmenter les performances du convertisseur par un choix approprié des paramètres du circuit de pilotage des transistors. En outre, les résultats évalués montrent comment le profil transitoire de la puissance demandée affecte le volume des solutions de conception optimales. Afin de démontrer la stabilité du système, la faisabilité des solutions de dimensionnement et le respect des contraintes et de la valeur des pertes attendues, un convertisseur de 3kW à hauts rendement et compacité correspondant à l'une des solutions a été conçu (Figure 8).

Figure 8 Prototype du convertisseur boost réalisé.

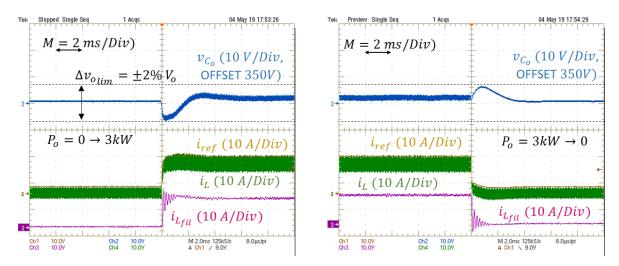

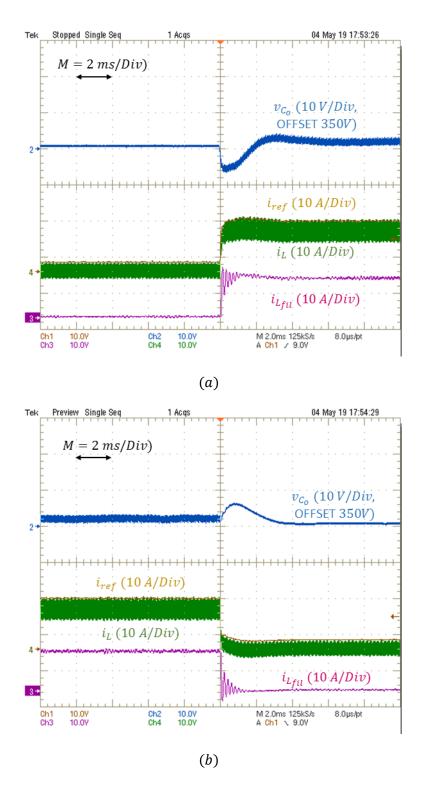

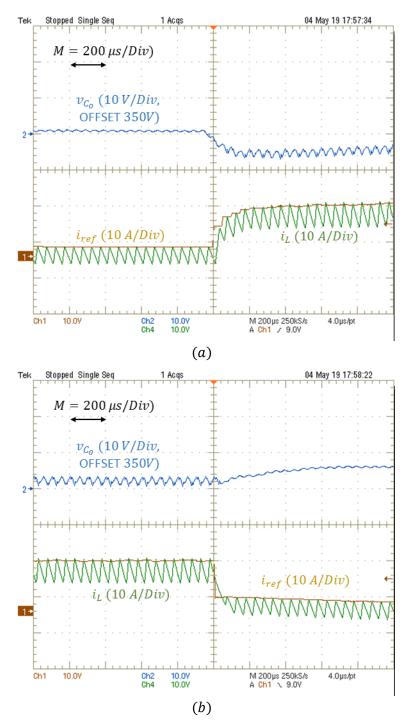

Figure 9 Formes d'onde de la tension de sortie  $v_{C_o}$ , courant de référence  $i_{ref}$ , courants des inducteurs  $i_L$  et  $i_{L_{fil}}$  pendant les transitoires de charge de montée et de descente.

Les tests expérimentaux confirment la conformité à toutes les exigences et, par conséquent, valident l'efficacité de la procédure d'optimisation proposée. Les performances du prototype du convertisseur boost montrent un bon accord avec les résultats attendus, tant en régime permanent qu'en régime transitoire. Le système contrôlé est stable et les formes d'onde montrent une conformité aux spécifications de tension et de courant lors d'une variation de la puissance de la charge, visible en Figure 9. De plus, les pertes de puissance mesurées confirment le modèle de pertes de puissance adopté.

## Contents

| A | ckno  | wledg   | gments                                                            | ii  |

|---|-------|---------|-------------------------------------------------------------------|-----|

| R | ésum  | né en I | Français                                                          | iv  |

| С | onter | nts     |                                                                   | xii |

| G | enera | al Intr | oduction                                                          | XV  |

| 1 | ]     | Power   | Electronics Systems for Embedded Applications                     | 1   |

|   | 1.1   | Intr    | oduction                                                          | 1   |

|   | 1.2   | Em      | bedded application in the transportation sector                   | 2   |

|   | 1.    | .2.1    | More Electric Aircraft (MEA)                                      |     |

|   | 1.    | .2.2    | EV/HEV                                                            | 6   |

|   | 1.3   | Nev     | w opportunities: Wide Band-Gaps Devices                           |     |

|   | 1.    | .3.1    | SiC and Si technology comparison                                  |     |

|   | 1.    | .3.2    | Unipolar and bipolar technology: MOSFET and IGBT                  | 14  |

|   | 1.    | .3.3    | Electro-magnetic Interferences (EMI) Issues                       |     |

|   | 1.4   | Cor     | nclusion                                                          |     |

| 2 | ]     | DC/D    | C Power Conversion in an Embedded Powertrain Application          |     |

|   | 2.1   | Intr    | oduction                                                          |     |

|   | 2.2   | DC      | /DC power converters for Starter applications in a MEA            |     |

|   | 2.    | .2.1    | DC/DC Step-up converters topologies                               |     |

|   | 2.    | .2.2    | DC/DC Step-up/down converters topologies                          |     |

|   | 2.3   | Pro     | posed QZS step up/down DC/DC converter topology and its modelling |     |

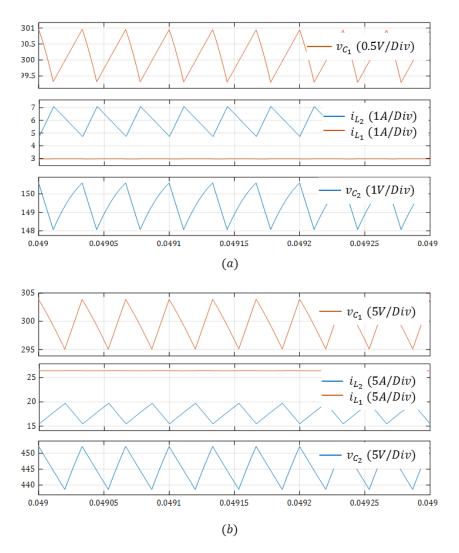

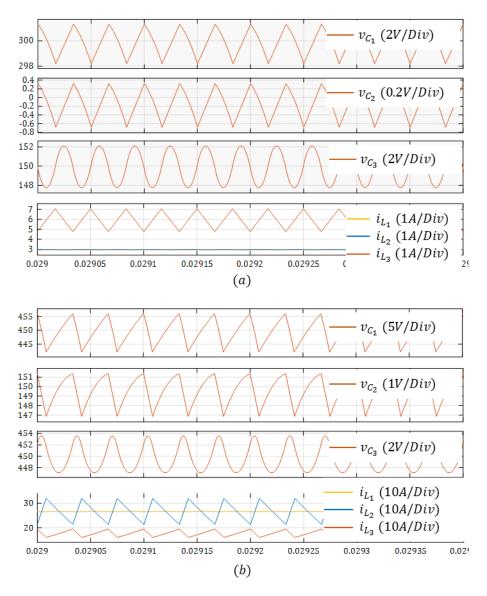

|   | 2.    | .3.1    | Operating principles                                              |     |

|   | 2.    | .3.2    | Input ripple suppression                                          |     |

|   | 2.    | .3.3    | QZSBC experimental validation                                     |     |

|   | 2.    | .3.4    | Comparison                                                        |     |

|   | 2.4   | Cor     | nclusions                                                         |     |

| 3 | ]     | DC/D    | C Power Converter Design                                          | 53  |

|   | 3.1   | Intr    | oduction                                                          | 53  |

|   | 3.2   | DC      | -DC Boost Converter Design                                        |     |

|   | 3.3   | Act     | ive components                                                    |     |

|   | 3.    | .3.1    | MOSFET conduction behaviour                                       |     |

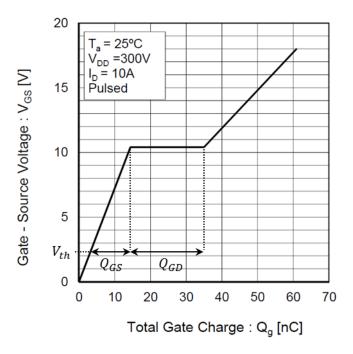

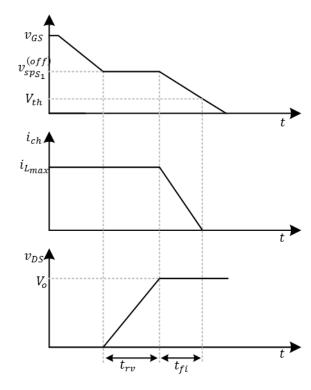

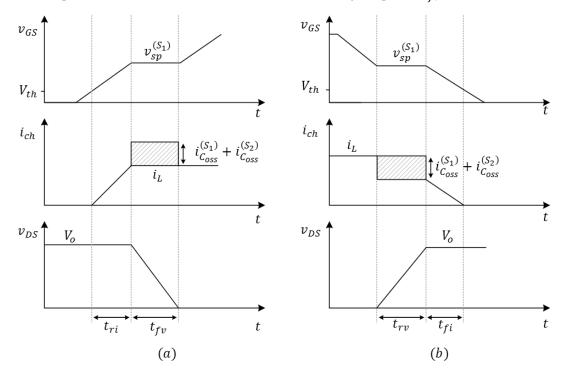

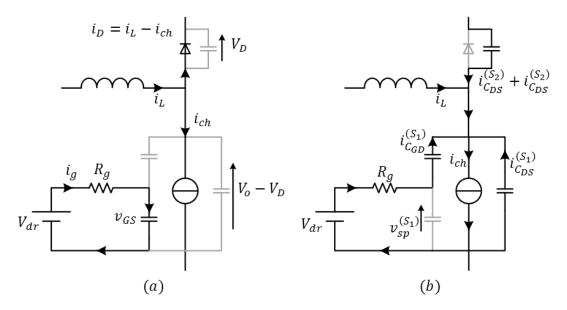

|   | 3.    | .3.2    | MOSFET switching behaviour                                        |     |

|   | 3.    | .3.3    | Freewheeling Diode                                                | 64  |

|   | 3.    | .3.4    | Thermal analysis                                                  | 64  |

|   | 3.4   | Pas     | sive Components                                                   | 68  |

|   | 3.4   | 4.1    | Magnetic component design                                                             | 68     |

|---|-------|--------|---------------------------------------------------------------------------------------|--------|

|   | 3.4   | 4.2    | Output Capacitor                                                                      | 75     |

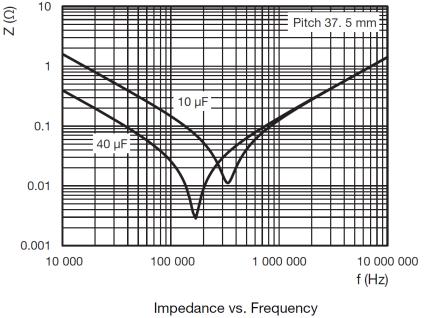

|   | 3.4   | 4.3    | EMI Filter                                                                            | 79     |

|   | 3.5   | Con    | clusions                                                                              | 84     |

| 4 | Γ     | Dynan  | nical Analysis and Control Strategy of a DC-DC converter                              | 87     |

|   | 4.1   | Intro  | oduction                                                                              | 87     |

|   | 4.2   | Dyn    | amical model of a DC/DC switched converter                                            | 89     |

|   | 4.3   | Boo    | st dynamical behaviour                                                                | 90     |

|   | 4.    | 3.1    | Frequency domain stability analysis                                                   | 90     |

|   | 4.3   | 3.2    | Boost dynamical analysis                                                              | 91     |

|   | 4.4   | Con    | trol strategy for power disturbance rejection                                         | 98     |

|   | 4.4   | 4.1    | Inner Loop: Peak Current Mode Control                                                 | 99     |

|   | 4.4   | 4.2    | Energy loop                                                                           | 101    |

|   | 4.5   | Cap    | acitor design for load transient rejection                                            | 104    |

|   | 4.    | 5.1    | Evaluation of the minimal value of <i>Co</i> in step-up load transient conditions     | 106    |

|   | 4.    | 5.2    | Evaluation of the minimal value of <i>Co</i> in step-down load transient conditions   | 108    |

|   | 4.    | 5.3    | Evaluation of the minimal value of <i>Co</i> for a smooth load transient condition    | 110    |

|   | 4.6   | Stab   | vility issues related to the insertion of the differential input filter               | 113    |

|   | 4.0   | 6.1    | Stability of cascaded sub-systems                                                     | 114    |

|   | 4.0   | 6.2    | Interaction between LC input filter and Boost converter: small-signals domain and 116 | alysis |

|   | 4.0   | 6.3    | Interaction between LC input filter and Boost converter: discrete time domain and 120 | alysis |

|   | 4.7   | Con    | clusions                                                                              | 124    |

| 5 | Ν     | Aulti- | Objective Optimization of a DC/DC Boost Converter                                     | 127    |

|   | 5.1   | Intro  | oduction: Optimization Problem                                                        | 127    |

|   | 5.    | 1.1    | Figure of Merits                                                                      | 129    |

|   | 5.    | 1.2    | Optimization problem: Design Variables Space and Performance Space                    | 130    |

|   | 5.    | 1.3    | Genetic Algorithms: NSGA II                                                           | 132    |

|   | 5.2   | Mul    | ti-objective optimization of a DC/DC converter                                        | 134    |

|   | 5.2   | 2.1    | Design Space and parameters                                                           | 136    |

|   | 5.2   | 2.2    | Objective functions                                                                   | 144    |

|   | 5.2   | 2.3    | Constraints Functions                                                                 | 145    |

|   | 5.2   | 2.4    | Optimization results                                                                  | 146    |

|   | 5.3   | Exp    | erimental results                                                                     | 149    |

|   | 5.4   | Con    | clusions                                                                              | 156    |

| G | enera | 1 Con  | clusions                                                                              | 157    |

| References |

|------------|

|------------|

## **General Introduction**

Due to the progressive shortage of fossil fuels and the environmental emergency, international agreements have been established to contain the global average temperature growth in the long term. The directives introduced aim to converge financial flows towards a climate-resilient development and to drive the efforts of the industrial community towards a low level of greenhouse gas emissions, especially in the transportation sector, which showed the highest increase rate of energy consumption (then of greenhouse gas emissions) in the last three decades.

The aeronautics and automotive industry moved toward more efficient and autonomous solutions, which led to a considerable electrification of the energy conversion systems on-board. The market of the electric vehicles or hybrid electric vehicles is in consistent growth. The energy exchange between the storage units, the powertrain actuation system, the internal combustion engine/generator and the numerous utility loads is carried through a DC network, and each source/load requires a specific converter to be interfaced on it. At the same time, in the electrical network of the modern aircraft network (More Electrical Aircraft), several mechanical units have been replaced by electrical counterparts, for the benefit of efficiency and weight of the overall system.

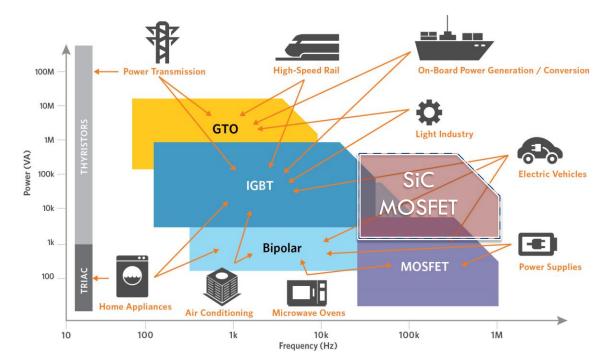

To supply the several power loads on-board, the power electronics units consist of switched-mode power converters whose operation take place through the switching of semiconductor transistors. The evolution of the power converters improves simultaneously with the technological progress of semiconductor devices. As explained in the first chapter, silicon-based devices dominated the market in the last three decades. For application within the power range of the order of hundreds of kW, the Insulated-gate bipolar transistor (IGBT) has been the most commonly used device because of its high current and voltage ratings (compared to the MOSFET unipolar devices). Nonetheless, due to the bipolar nature of the IGBT structure, the operating switching frequency of the power converter, when this device is employed, is limited by the commutation times of the device. On the other hand, research on wide band-gap (WBG) semiconductor materials has led to the introduction of new high-performance devices mature enough to make their way into the market. The features of the WBG materials like Silicon-Carbide or Gallium-Nitride allow building unipolar devices, like metal-oxide-semiconductor fieldeffect transistor (MOSFET), with the same current and voltage ratings of the off-the-shelf IGBTs, higher operating temperature, lower conduction losses and faster commutation times. The possibility to significantly increase the switching frequency while keeping power losses low leads to an overall improvement of the conversion system in terms of efficiency and size of the passive elements and the cooling system. The spread of such devices offers clear opportunities to considerably improve the conversion power electronics systems.

The electrical micro-grids in embedded applications, such as HEV/EV or modern aircrafts, are composed by several electric loads and sources connected to a common voltage bus. The electrical power is usually provided by generator units powered by the combustion engine and storage units (batteries or super capacitors). The maximal power flow in this grid is comparable to the power of the most demanding loads. In case of large variations of the power demanded by the most powerful loads, the voltage provided by the storage units may exhibit a significant variation. This variation affects the design of the several loads connected to the network and usually leads to an increase in volume and mass of the entire embedded system.

The first example concerns the electric energy distribution network aboard a modern aircraft. It is composed of an AC voltage bus and a DC voltage bus supplied by the AC network through rectifier units. In the specific case of the More Electrical Aircraft, the most remarkable evolution is the suppression of the gearbox unit (IDG for Internal Drive Generator), which ensured a fixed mechanical speed for each network connected generator, regardless of the highly variable speed of the engine. In absence of the IDG, the aircraft electrical generation systems are more reliable, but the 3-phase AC

networks have a variable frequency as well as a variable voltage amplitude. The variable amplitude and frequency of the AC voltage causes a consistent variation in the DC bus voltage obtained by rectifier units. Then, the electrical and mechanical loads are supplied by DC/DC or DC/AC (depending on the load) converters connected to variable DC bus voltage.

Similar issues can affect the electrical network of electrical or hybrid electrical (EV/HEV) vehicles, where the DC bus may exhibit large variations because of the non-ideal features of the storage units.

In this context, the efficiency, the size and the level of integration of the power electronics conversion are primary goals to attain. For an embedded powertrain application, the power electronics stage is often composed of just an inverter connected to the DC bus through an input filter, which supplies a polyphase electrical machine. The DC bus voltage variations affects the motor turn number and its rated current, then the inverter power losses and the inverter cooling unit as well. Indeed, if the drive chain is only composed of the inverter and input filter, the motor stator windings should be designed to operate to ensure the controllability of the motor torque for the whole range of variation of the DC bus voltage value, resulting in increased power losses in the inverter and a consequent oversizing of its active components and cooling unit. As explained in Chapter 2, an interesting alternative to avoid these constraints is to insert a DC/DC converter between the filter and the inverter. This solution helps the inverter's immunization against the voltage disturbances on the DC bus, especially in the case of an electric network in a modern aircraft or in electrical or hybrid vehicles. The additional DC/DC converter offers the possibility to optimize the actuation chain efficiency in the whole operating speed range. Depending on the speed requirements, the best solution could be a step-up, a step-down or a stepup/down converter (for a wide speed range). In Chapter 2, the most common DC/DC converter topologies for such application are presented. For the specific case of wide speed range applications, an original step-up/down topology is presented and analysed.

The major requirements for the described motor drive application are clearly compactness and efficiency of its constituents. However, the design problem of a DC/DC converter is not a trivial task, especially when it comes to optimizing multiple performances. Several variables relative to each component are involved, which belong to different engineering domains (electrical, magnetic, thermal...). Moreover, most variables are inextricably linked to each other. To attain different goals (efficiency and compactness), the designer should have a comprehensive knowledge of the influence of each design variable, in order to make the appropriate trade-offs and comply with the feasibility and application constraints. It should be remarked that the design parameters are limited to the availability of the components on the market. In Chapter 3, the design problem of a DC/DC power stage (boost converter and input filter) is described for each element. The analytical models employed and the relative variables and parameters are presented in order to understand the compromises involved in the design of the power stage of the converter.

One aspect often considered only after the design of the converter power stage is the dynamic behaviour of the converter, such as the response to a variation in the operating point or a disturbance, such as load variation or DC-bus voltage variation.

In the considered powertrain applications, if the motor torque, then the motor phase current references, need to increase quickly, the motor phase currents will rapidly increase as well, due to wide bandwidth of the current control loops. Under such condition the inverter power step could cause a drop of the DC/DC converter output voltage, which may affect the controllability of the phase currents. The dynamical response of the DC/DC converter output voltage to power load variations does not depend exclusively on the control strategy and its parameters, but also on the power stage components and parameters, such as the passive components and the switching frequency. As discussed in Chapter 4 through fundamentals of linear system theory, the passive elements of the controller and the system stability. Furthermore, due to the practical limitations of the regulators (finite bandwidth, command signals saturation), the excursion of the passive components' currents' currents' currents' control be reduced below a certain level. Passive components should be specifically designed to ensure full

compliance with the input and output terminal excursion requirements of the application during any variation of the operating point scheduled in the mission cycle.

For the case under study, the control strategy has been chosen specifically for the rejection of the power load variations. Once the control strategy and the controller parameters have been defined, the closed loop system stability can be analysed, especially when an input filter is required for the input current harmonics to meet the standards imposed by the application. In fact, the interaction between two cascaded stable subsystems, as in the case of the input filter and the converter, can lead to instability. The stability issues of the system composed by the converter and the input filter are discussed in Chapter 4 as well.

While optimising the compactness and efficiency of the converter's power circuit alone was a nontrivial task, it is even more complicated if the dynamic behaviour is taken into account, including the control strategy and the respective parameters. In order to address the numerous variables and parameters involved in the optimization problem (of both power stage and controller), a multi-objective optimization tool has been developed in Chapter 5. Thanks to the proposed procedure, the most convenient design solutions in terms of efficiency and compactness are identified.

Besides the steady state behaviour, the developed algorithm takes into account the dynamic of the converter during the variation of the load power. This means that the evaluation of the solutions involves the selection of the power stage and regulator parameters at the same time, ensuring an optimal design that is able to meet the specifications both in steady state and in transient behaviour. Furthermore, the stability of the system composed by the converter, the load and the input filter is ensured as well. A 350V/3kW test bench has been implemented to validate the reliability of the models employed in the routine and to verify the compliance with the design specifications of the converter prototype in steady state and load transient.

## 1 Power Electronics Systems for Embedded Applications

#### 1.1 Introduction

This chapter is meant to introduce the context of this work. The main objective of the thesis is to propose a design approach for a DC/DC converter. The converter is part of the conversion chain for the power supply of an on-board actuator. It has been conceived more specifically for embedded applications in the transportation sector, namely hybrid/electric vehicles and modern aircrafts.

The design targets depend on the requirements of these applications, hence it is fundamental to properly introduce the context in which the design procedure will be developed.

In embedded systems, especially in the domain of the transportation sector, the current trend, due to both the shortage of fossil fuels and the new international agreements for the resolution of pressing environmental issues such as pollution and climate change, is to reduce the green-house gas emissions.

Moreover, in on-board electrical systems, as in the most aircraft electrical networks, several hydraulic, pneumatic or mechanical parts have been replaced by electrical counterparts, which leads to a remarkable gain in terms of size, weight and wasted power.

Since the storage systems and the utility power loads on-board operate at DC voltages, the design of the DC conversion chain within the electrical micro-grid embedded architecture gained a particular attention. In this context, the main elements of the electrical grid in electrical and hybrid electrical vehicles and modern aircraft are described in the following.

Currently, the electrical network on-board in most vehicles includes at least one DC bus, in which the DC/DC conversion is largely employed, as it will be showed in the following. The current tendency is to push the operating voltages toward higher values, which leads to a significant gain in terms of efficiency and size of the conversion system.

In order to follow the increasing trend of power electrical need, the on-board converter should be designed as small and as efficient as possible, so to lighten the conversion chain and reduce the fuel consumption. The achievement of such objectives could be pretty challenging, especially when the design problem is constrained by the ripple requirements set by the aeronautics or automotive standards. The energy storage or supply devices, indeed, may vary their output voltage in response to variation of the load or their state of charge. Such variations should comply with the requirements of the standards in order not to compromise the normal functioning of the other devices connected, or even the stability.

In the last decade, the availability on the market of wide band-gap semiconductor devices strongly contributed to the efficiency and the compactness of switched converters, particularly in view of the increase of the voltage values involved. The superior features of these devices provided the opportunity to develop power converters with performances never reached before. Their benefits over the widespread and mature classical devices are discussed in this chapter, and the performances are validated on an experimental test-bench.

#### 1.2 Embedded application in the transportation sector

In recent years, fossil fuel shortage and environmental pollution moved the research community toward more efficient and alternative solutions in the energy conversion field. In order to cope with climate change due to harmful and increasing gas emissions due to the widespread use of fossil fuels, the power and traction architectures of the main transport systems have been revised and improved. The increasing usage of conventional combustion engines is causing harm to the environment and health itself, as these engines burn petrol, diesel or natural gas and produce carbon dioxide ( $CO_2$ ), Sulphur dioxide ( $SO_2$ ) and oxides of nitrogen ( $NO_x$ ) as harmful exhaust components.

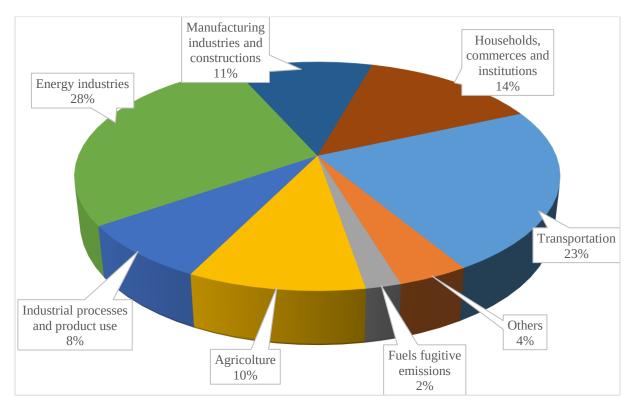

As stated in the 2019 annual report by European Environment Agency's European Topic Centre on Climate Change Mitigation and Energy, in the EU, the transportation sector alone is accountable for approximately a quarter of greenhouse gas emissions as illustrated in Fig. 1.1 [1]–[3].

Fig. 1.1 Greenhouse gas Emission reported for the 2019 [4].

Furthermore, it has been registered that greenhouse gas emissions decreased in the majority of sectors between 1990 and 2017, with the notable exception of transport sector, including international transport, refrigeration and air conditioning. The energy consumption, hence the emissions, in the transportation sector exhibited an increase up to 36% in the same period [1], [3], [5], [6].

In order to satisfy the climatic target and the regulations imposed by the international agreements, such as the "Paris Agreement" in 2015 and the "Doha Amendment to the Kyoto protocol (2012)", more electrical alternatives are replacing the conventional drive traction and on-board power supply systems. This imposes new challenges for energy generation, conversion and delivery tasks in the on-board power grid of the means of transport, which lead to the rapid penetration of power electronics systems.

The research effort recently focuses basically into finding miniaturized, lightweight, highly power dense solutions. This allows a reduction in the installation cost, and an improvement of the autonomy of the vehicle. In the following sections, it will be shown the fundamental role of the power electronics conversion in two largely discussed embedded applications, such as the aerospace and the hybrid-

electric vehicles, with a clear emphasis on the role of the DC-DC conversion, which is the subject of this thesis study.

#### 1.2.1 More Electric Aircraft (MEA)

Over the last few decades, there has been tremendous progress and efforts to move toward more electric aircraft (MEA). Considerable effort has been spent in the intensive development of the electrical system on-board of large civil aircraft by Boeing and Airbus, or military aircraft (F-22 or F-35). The MEA has ambitious objectives in the coming years such as reducing fuel consumption and the emissions of noise and gas ( $CO_2$ ,  $O_x$ ). It has been estimated, indeed, that 1 kg saved on each flight could save about 1,700 t of fuel and 5,400 t of  $CO_2$  emissions per year for the recent air traffic. In addition, a decrease in mass would also result in a significant gain in cost: every additional kilogram of system costs approximately 1,000 \$ [7].

In a MEA, the electrical power supplies the non-propulsive aircraft systems/loads, which are typically driven by a combination of different secondary power types such as mechanical power, pneumatic and hydraulic and so on [8]–[11]. Currently, for example, the environmental conditioning is supplied through a bleed air system [11], [12], which provides pneumatic power directly drawn from high-pressure hot air extracted from aircraft engines. The removal of the pneumatic system eliminates the need for a bleed air system embedded on the gas turbine, which leads to a significant improvement in the efficiency of the turbine. Other types of loads (braking, pumps) that were earlier powered by hydraulic networks were replaced by electrical loads [13]. As for hydraulic energy, it comes from a hydraulic pump driven by the internal combustion engine. This energy is mainly used to operate the flight controls, the undercarriage and braking systems.

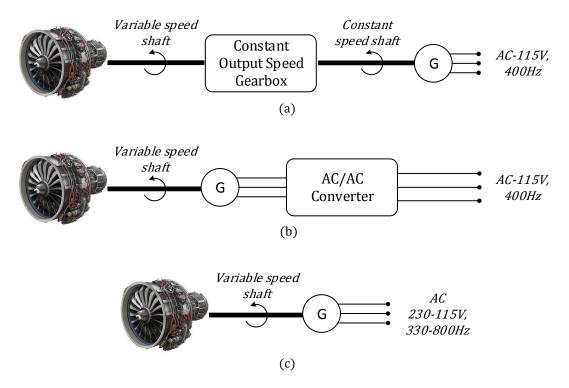

The removal of the mechanical and hydraulic systems allows a remarkable reduction of the overall system size. Furthermore, the employ of electrical system remarkably improves the prognostic and diagnostic functions of the system [7], which allows reducing the maintenance time and cost of the aircraft. The first aircraft generations were equipped with fixed frequency (400 Hz) integrated drive generators (IDG), as shown in Fig. 1.2(a). One of the important steps toward the electrification of the aircrafts was the substitution of the IDG by a variable frequency generator. The use of such generator allowed removing the heavy and expensive gearbox system employed to provide the constant frequency.

Two alternative solutions have been proposed. The first option is depicted in Fig. 1.2(b) and consists in a Variable Speed Constant Frequency (VSCF) DC link system [15]. The electrical power supplied by the gas turbine is transformed by a back-to-back frequency converter and brought to a constant frequency of 400 Hz. The AC/AC converter can be realized using several topologies, such as matrix converters, cycle-converters, or back-to-back inverters [16], [17]. The advantage of this solution consists in providing a voltage waveform similar to the classical configuration (115V, fixed 400Hz frequency), which allows to easily adapt the existing loads available on the market. Nevertheless, the presence of the frequency converter implies additional losses and weight, not to mention decreasing the reliability of the system.

Another configuration, as shown in Fig. 1.2(c), represents the preferred solution for recent military and commercial aircraft applications (Boeing 787, Airbus A380), since it is generally characterized by simplicity and reliability. It consists in using directly the AC electrical power provided in a range of frequencies [330Hz;800Hz] and a nominal voltage of 115V or 230V AC [17]. Since most of the electrical aircraft loads requires a controlled constant frequency power supply, the variable-frequency supply cannot be used directly for most applications. That means every load needs its own power converter: this system could be considered non optimal in terms of mass and cost, but it brings several advantages concerning the safety and the failure detections of the single loads [18], [19].

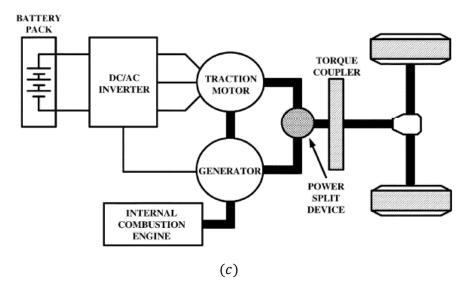

An example of electric grid on-board is shown in Fig. 1.3.

Fig. 1.2 Evolution of the AC electric generation and distribution network [14].

Fig. 1.3 Example of on-board electric grid supplied by a variable speed variable frequency generator [7].

The VSG (Variable Speed Generator) supplies the AC bus with variable frequency and voltage. A conventional aircraft grid is based on a main bus voltage of 115 V AC, but, recently, some newer developments use 230 V AC [7], [17].

Most of the power loads on-board are supplied by a DC voltage, generated from the AC bus through a rectifier unit. The trend is to use a DC link of 270 V ( $\pm$ 135 V) or 540 V ( $\pm$ 270 V), respectively generated from a 115 V AC or 230 V AC, 330–800 Hz through an auto-transformer rectifier unit (ATRU). For a

DC network with a nominal voltage of 270VDC, it can vary from 230V to 335V because of the variable amplitude of the AC voltage generated by the VSG. A lower voltage bus of 28 V DC is employed to supply the minor loads.

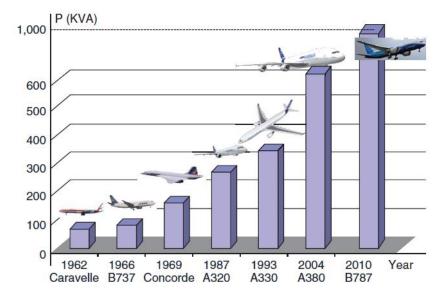

Fig. 1.4 Electrical power demand trend in commercial aircrafts [7].

Fig. 1.4 shows the increasing evolution trend of the electrical power need of a common aircraft over the last fifteen years. With respect to the increase of the loads' power, the trend moved toward high voltage DC network (HVDC). HVDC-grids provide indeed several benefits. The main advantages are manifold.

The current levels are lower (10 times compared to the 28 V DC bus) than the conventional low voltage levels. Hence, the cross-section of the wires can be considerably reduced, as well as the weight.

With the increasing number of power electronic loads, a MEA with a classical AC network would include a high number of AC/DC rectifier stages. A more suitable interface between the grid and the DC loads allow to reduce the weight and the efficiency of the DC/DC conversion systems.

The HVDC network, furthermore, would ease the voltage coupling between the loads and the generator, with possible regenerative load acceptance [20].

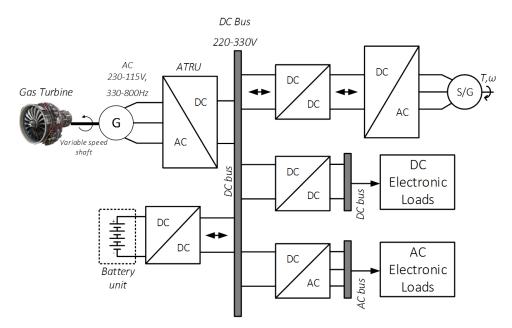

A simplified example of the DC power distribution architecture of the DC link system in a MEA is shown in Fig. 1.5. A battery unit is employed primarily to support the starting process of the engine and to power the auxiliary units, or as emergency backup power for equipment and instruments.

The grid showed in Fig. 1.5 consists of a battery storage system, 270 V DC power distribution bus, AC and DC loads and the respective converters. The power generation block consists of the engine Starter/Generator set: it provides the electrical power to the distribution bus, thus powering the electrical loads, during the generation phase. It is connected to the bus through a bidirectional DC/AC inverter, usually decomposed in a DC/DC converter and a Voltage Source Inverter (VSI) inverter. Another bidirectional DC/DC converter interfaces the battery unit with the DC bus. Unidirectional DC-DC converters are commonly used in the grid to supply other utility loads or to 28 V DC and a DC-AC converter is used for conversion to 115 V AC. All the conversion stages shall be designed carefully in order to meet the volume, weight and efficiency requirements for aeronautics applications. Furthermore, they must satisfy the aviation standard, such as DO-160 or MIL-704, which set the harmonic emission standards [11], [21]–[23].

Fig. 1.5 Example of DC micro-grid on-board in a MEA.

#### 1.2.2 EV/HEV

Similarly to the aeronautics field, the automotive industry, pushed by the demands of higher fuel economy and more electric power, is moving toward an evolution of the electrical power systems. Several functions that were traditionally led by mechanical, pneumatic, and hydraulic systems, are now increasingly being replaced by the electrical systems, in order to increase the performance and efficiency [4], [24]. Furthermore, the electrical demand on-board strongly increased because of the introduction of a wide range of new functionality in vehicles. Indeed, the rate of increase of automotive loads is about 4% per year [25].

Due to cost reasons, the market and the industry have recently focused on the production of hybrid electric vehicles (HEV), rather than pure electric vehicles (EV). Between the innovative solutions, it is worth mentioning the fuel cell propulsion system, which represents an interesting alternative compared to the EV, especially for the emission benefits. Nevertheless, the widespread of fuel cell powered systems is impeded by the high production costs and the limited spread of supporting infrastructures and refuelling stations.

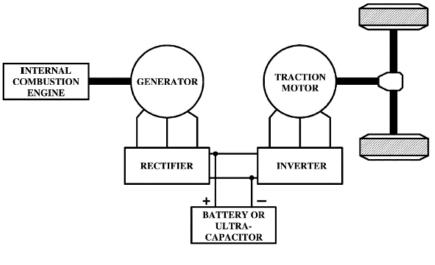

Hybrid vehicles have two or more energy sources. In a HEV the traction is partially sustained by the combustion engine and partially by a battery unit or a super capacitor unit, depending on the configuration [3], [25].

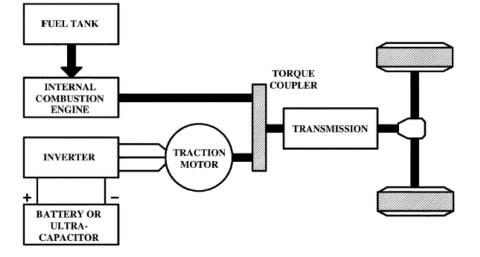

In Fig. 1.6, three among the most used architectures of a HEV powertrain architecture are depicted.

The series configuration Fig. 1.6(a) is the closest one to a pure electric vehicle architecture, where the thermal engine is employed to charge the propulsion batteries/super-capacitor bank on-board the vehicle. The power flow is converted twice by a generator upstream the battery bank and an inverter connected to the electric motor. Contrary to the series set up, the engine/generator in the parallel Fig. 1.6(b) and series/parallel Fig. 1.6(c) configurations is mechanically connected to the transmission block. The advantage of the series HEV configuration is that the fuel engine runs mostly at its optimal combination of speed and torque, having a low fuel consumption and high efficiency. On the other hand, the double conversion stage between the fuel engine and the transmission can cause an important loss of energy. Hence the development of the others configuration, which improve the overall drive train efficiency.

(*b*)

Fig. 1.6 HEV series (a), parallel (b) and series/parallel (c) architectures [26].

Generally, a series hybrid is preferred when the mission cycle includes frequent start/stops, typically for city employ. A parallel hybrid vehicle offers lower fuel consumption in the highway driving cycle, in which the vehicle is mostly running at constant speed.

In Fig. 1.7 an example of a typical micro-grid architecture on-board is shown [24]. The continuous increase in power requirements motivated the development of both higher-power and higher-voltage electrical systems. The DC bus voltage levels moved from the conventional values of 6V, 12 V to 300V and higher values [27].

The architecture scheme is pretty similar to the one presented for the MEA case. A common use is to employ at least two DC busses, a high voltage (150/300V) main bus for high power loads, and a lower voltage bus for minor DC loads (14/42V) [28].

Fig. 1.7 HEV electrical grid example [26].

Unidirectional DC-DC converters supply various low power loads such as sensors, controls, entertainment, utility, and safety equipment. Bidirectional DC-DC converters are used in places where battery charging, regenerative braking, and backup power are required. As a backup power system, the bidirectional DC-DC converter facilitates the safe operation of the vehicle when the internal combustion engine or the electric drives fail to drive the motor. Due to the aforementioned reasons, high power bidirectional DC-DC converters have recently gained a lot of importance. Research in wide band-gap devices is mature enough to attain the increasing demand of small-sized, reliable, lightweight, controllable and efficient DC-DC converters in automotive industries.

#### 1.3 New opportunities: Wide Band-Gaps Devices

It is clear from the review that, in the ranges of voltage and power involved in micro-grid structures for mobile applications, the DC-DC converters are leaning towards fast switching active components.

Therefore, semiconductor materials that help to achieve a higher switching speed that does not correspond to an excessive increase in thermal losses are preferred. Thus, Wide Band-Gap (WBG) materials are quickly becoming the mainstay of high-power and high-speed.

Based on the consideration developed in the previous sections, DC-DC power converters for aeronautics or EV/HEV applications require powerful, compact, and reliable electronic devices in order to facilitate power system integration. In a Switched Mode Power Supply (SMPS), the nature of the semiconductor devices has a heavy impact on the design and the performances of the whole converter.

In most of the switching applications Metal-Oxide Semiconductor Filed Effect Transistor (MOSFET) and Insulated Gate Bipolar Transistors (IGBTs) are predominant than the other switching devices due to the easy driving ability and their specific features (respectively high-power ratings and fast switching behaviour).

These applications include Uninterruptable Power Supplies (UPS), Solar Inverters and Converters, various motor driver systems, Pulse Width Modulation (PWM) technique-based applications, SMPS etc.

Fig. 1.8 Power/frequency application ranges of the common power devices [29].

For high voltage applications, the silicon Si IGBT has been the dominant power semiconductor device in low and medium frequencies power conversion applications, in power ranges from the kilowatt to the megawatt. In the last 30 years, the research results brought the development of Si IGBT and free-wheeling diode technology to a high level of maturity [30]. The incremental improvements in performances obtained with each new generation of IGBT technology are becoming ever smaller, hence the need of an alternative to the Si technology. Further developments of the performance of Si-based semiconductors is limited by their physical properties and characteristics. The employ of Si-based semiconductors limits indeed the converters efficiency and allows a maximum switching frequency up to 30 kHz, which lead to a limited power density [4], [31]–[33].

The recent advances in WBG technology has created great opportunities for increasing the efficiency and the power density of the conversion chains. Contemporary researches found that silicon carbide (SiC) semiconductors are highly suitable for designing high power DC-DC converters due to its capability for handling vast power ranges up to 100 kW [31]. Most important, SiC features allow to build extremely fast devices able to remarkably increase the operating switching frequency, which brings drastic improvements in the power density of the converter. At the same time, the GaN, is considered as the future low-cost device [34], [35], even if it still is not mature enough. Its growth in high power applications is currently hold back by several technological constraints, such as packaging and reliability.

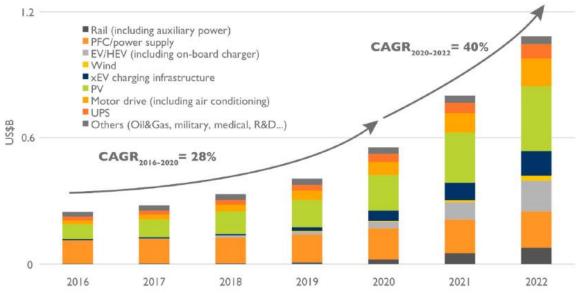

Fig. 1.9 WBG growing market [36].

With the rapid technology innovations and continued advancements in the semiconductor industry, SiC-based power devices have evolved from immature prototypes in laboratories to a viable alternative to Si-based power devices. Many SiC power devices in the kV range are being investigated, such as SiC PiN diodes, Schottky diodes, JFET, BJTs and various MOSFETs. An investigation, carried out by the Yole Developpement Institute [36], concerning the market trend analysis of the WBG devices show a consistent increase of the market profits, as shown in Fig. 1.9, and estimated future revenues are as promising as they have been so far.

#### 1.3.1 SiC and Si technology comparison

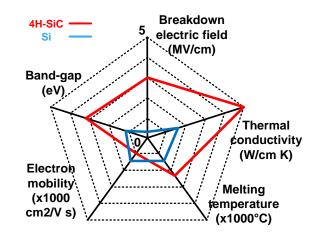

Silicon carbide (SiC) potentially offers several advantages over conventional silicon (Si) for use in power electronics devices. Comparatively, individual SiC materials (in theory) can endure temperatures up to 300°C (standard Si is typically limited to 150°C), withstand higher voltage for the same width, tolerate a larger current density, and operate at a higher frequency [37]. Indeed, in switching conditions, SiC MOSFETs show reduced conduction losses and allows low power switching losses. The enhanced efficiency can lead to reduction of cooling requirements and heatsink volumes. Moreover, the better dynamic performance of SiC-based devices allows to obtain high operating frequencies with consequently reduction of weight and size of the power converters' passive components (inductors, capacitors). Furthermore, the increase of the maximal operating temperature of the semiconductor device junction can improve the reliability of the system. Nevertheless, the operating temperature, for MOSFETs and IGBTs, is rather limited by the gate oxide that, contrarily to the JFET, limits the usage to 175°C. Power devices based on SiC have many advantages for high performance (high voltage, high current density, high temperature and high efficient) power electronics converters related to inherent material properties [31], [37].

The main benefit of silicon carbide (SiC) compared to silicon (Si) from a physical point of view is the larger band gap energy (varying from 2.37 eV for 3C-SiC to 3.26 eV for 4H SiC at room temperature). Particularly, the band gap of the most commonly used polytype (4H-SiC) is 3 times larger than silicon, which allows high temperature operations and low leakage current in reverse voltage condition.

Fig. 1.10 Comparison of the mean features of Si and 4H-SiC materials [37].

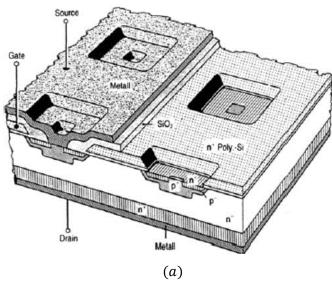

Fig. 1.11 3D(a) and cross section (b) of a npn MOSFET structure on a semiconductor wafer [39].

The higher thermal conductivity allows more heat to be dissipated from the SiC based device and a smaller temperature difference with the environment. Moreover, a high critical electric field, an order of magnitude greater than silicon (2.5 MV/cm for SiC-4H against 0.2 MV/cm for silicon). This level of

critical field enables the realization of drift layers with very low specific resistance, as compared to silicon, and therefore of unipolar components (JFET, Schottky diode, MOSFET) with very low series resistance [38].

In Fig. 1.11, the resistive path of the carriers is showed within a MOSFET topology. In the ohmic operating mode of the MOSFET ( $V_{DS} \ll V_{GS} - V_T$ , with  $V_T$  the gate-source threshold voltage), which is the operating zone of a power switching device, the drift region stands for the most part of the resistance ( $R_{epi}$  in Fig. 1.11(b)), or also called epitaxial region (since it is produced by epitaxy process). The conduction on-resistance can be approximated as in [31]:

$$R_{on} \cong R_{epi} = \frac{4(V_B + V_{bi})^2}{A\,\mu\,\varepsilon\,E_{max}^3} \tag{1.1}$$

where  $V_{bi}$  is the built-in potential,  $\varepsilon = \varepsilon_0 \varepsilon_r$  is the permittivity of the wafer,  $E_{max}$  is the critical electric field of the semiconductor, A is the conduction section of the drift area,  $V_B$  is the drain-source breakdown voltage of the device in off-state and  $\mu$  is the drift region mobility (in an N-Mosfet  $\mu = \mu_n$ , with  $\mu_n$  the electron mobility).

Table 1.1 shows the difference between the values of the defined quantities for both Si and SiC materials [31].

Table 1.1 Features of the Si and 4H-SiC materials [39].

|                                                             | SI                  | 4H-SIC              |

|-------------------------------------------------------------|---------------------|---------------------|

| Bandgap (eV at 300°K)                                       | 1.12                | 3.2                 |

| Critical Electrical Field (V/cm), $E_{max}$                 | $2.5 \times 10^{5}$ | $2.2 \times 10^{6}$ |

| Thermal Conductivity (W/cm K at 300°K), $G_{th}$            | 1.5                 | 3 - 4               |

| Relative dielectric constant, $\varepsilon_r$               | 11.8                | 9.7                 |

| Electron Mobility (cm <sup>2</sup> /V s, at 300°K), $\mu_n$ | 1420                | 1000                |

As evaluated in [40], it is possible to remark that the ratio between the conduction losses through a Si and a SiC device (at 423°K and 600 V,  $\mu_{n(SiC)} = 148 \ cm^2/(V \ s)$ ,  $\mu_{n(Si)} = 576 \ cm^2/(V \ s)$ ) where the devices are supposed to have the same conduction section A and designed for the same breakdown voltage  $V_B$  (valid just for high breakdown voltages [41]), corresponds to the ratio between the on-resistances:

$$P_{R_{on}} = R_{on} l_{rms}^2 \tag{1.2}$$

$$\frac{P_{R_{on(Si)}}}{P_{R_{on(SiC)}}} = \frac{R_{on(Si)}}{R_{on(SiC)}} \cong \frac{R_{epi(Si)}}{R_{epi(SiC)}} = \frac{\varepsilon_{r(SiC)}\mu_{n(SiC)}E_{\max(SiC)}^3}{\varepsilon_{r(Si)}\mu_{n(Si)}E_{\max(Si)}^3} = 162.69$$

(1.3)

In the mentioned conditions, the SiC devices exhibit far lower conduction losses, thanks to their intrinsic features ( $\varepsilon_r$ ,  $\mu_n$ ,  $E_{max}$ ).

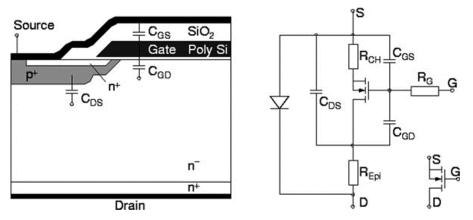

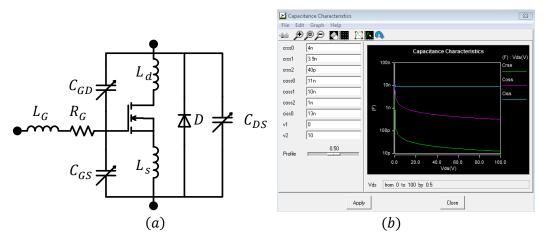

The mentioned features result in a remarkable improvement of the dynamical characteristics too. The dynamic behaviour of the MOSFET switching device is due to the intrinsic capacitances between the three terminals of the device, as shown in Fig. 1.12.

Fig. 1.12 Lumped parameter model of a MOSFET [39].

Their values determine the charging and discharging time of the gate terminal voltage, as well as of the  $v_{DS}$  voltage. It is clear that a smaller capacitances implies smaller time constants, hence shorter commutation times. The capacitance values are proportional to the section of the electrodes, hence to the dimensions of the semiconductor wafer, hence the *A* value. At the same on-resistance value  $R_{on}$  (i.e. same conduction losses) and the same breakdown voltage  $V_B$ , the ratio between the wafer sections *A* of the Si-based and SiC-based devices is given from (1.1):

$$\frac{A_{(si)}}{A_{(sic)}} = \frac{\varepsilon_{(sic)}\mu_{n(sic)}E_{\max(sic)}^3}{\varepsilon_{(si)}\mu_{n(si)}E_{\max(si)}^3} = 162.69$$

(1.4)

It is clear that the SiC technology implies a great benefit in terms or dynamical behaviour too.

These features can be resumed by the specific on-resistance S of the power device, expressed as the on-resistance/area product [30]:

$$S = R_{on}A = \frac{4(V_B + V_{bi})^2}{\mu_e \varepsilon_0 \varepsilon_r E_{max}^3}$$

(1.5)

The *S* value addresses indeed the trade-off between the  $R_{on}$  conduction resistance and the cross conduction section *A*, hence the intrinsic capacitances values. Thus, it can be seen as a compromise between the conduction losses and switching losses of the device. The smaller the *S* value, the more efficient the device in term of power losses.

Another approach to compare the relative performances two different devices was introduced in [30]. It consists of a widely used figure of merit, called Baliga figure of merit, and it is defined as:

$$F_M = \varepsilon_r \mu E_{max}^3 \tag{1.6}$$

The value  $F_M$  addresses the ratio between the square value of the breakdown voltage  $V_B$  and the onresistance of the device  $R_{on}$ . The ratio between the two figures of merits results in (1.7) and confirms the superiority of the SiC technology:

$$\frac{F_{M(Si)}}{F_{M(SiC)}} = 0.0025$$

(1.7)

In terms of reliability, the increase of temperature  $\Delta T$  in the device due to the conduction losses is defined as:

$$\Delta T = \frac{h}{G_{th}A} P_{R_{epi}} \tag{1.8}$$

Where  $G_{th}\left[\frac{1}{K_{m}}\right]$  is the thermal conductivity of the semiconductor, *h* and *A* are the thickness and the cross-section of the semiconductor thermal path, respectively, and  $P_{R_{ept}}$  is the wasted power.

Under the assumption of equal dimensions of the devices and equal Joule losses, the ratio between the temperature increments is equal to the inverse ratio of the thermal conductivities [40]:

$$\frac{\Delta T_{(Si)}}{\Delta T_{(SiC)}} = \frac{G_{th(SiC)}}{G_{th(Si)}} = 2.3 \tag{1.9}$$

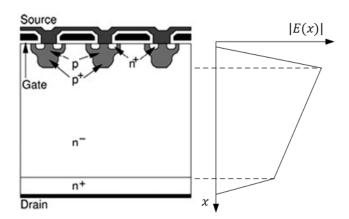

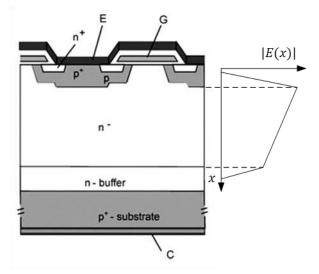

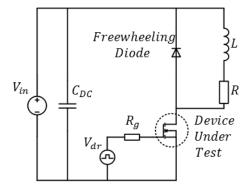

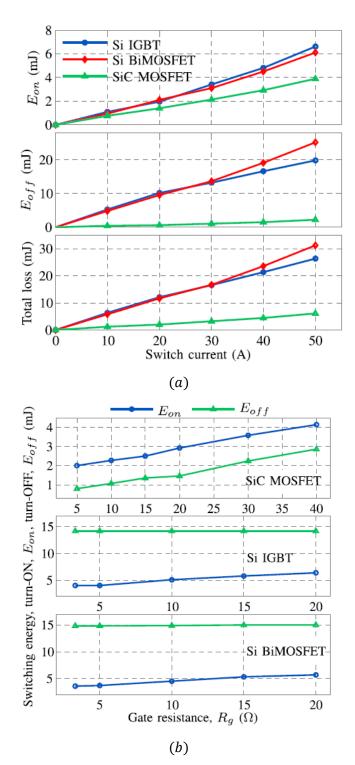

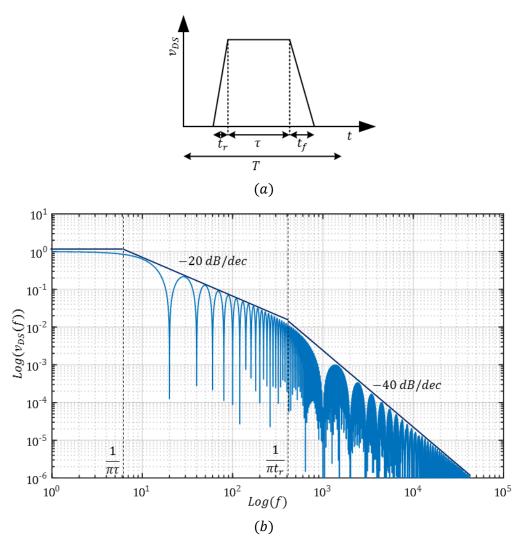

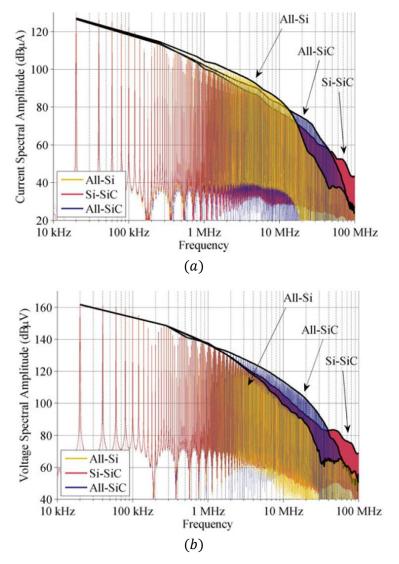

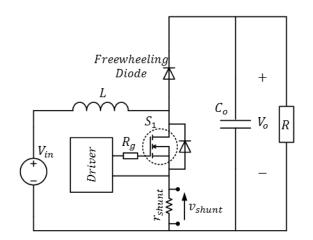

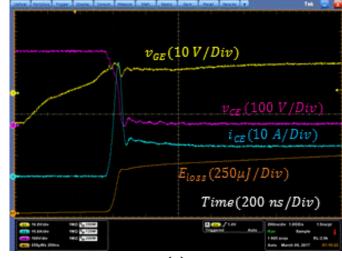

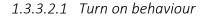

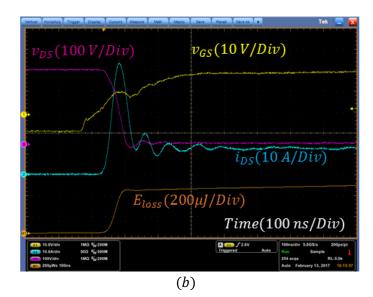

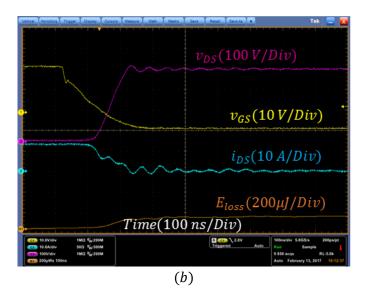

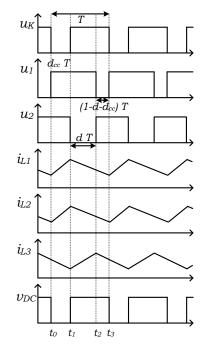

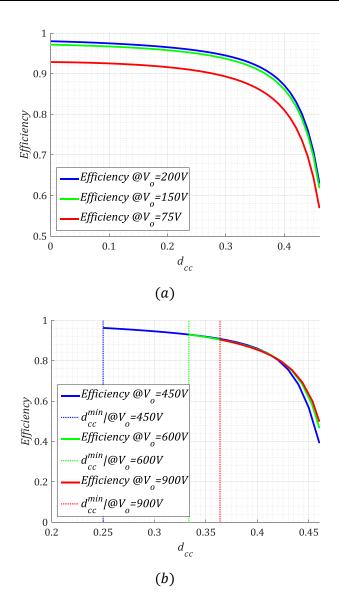

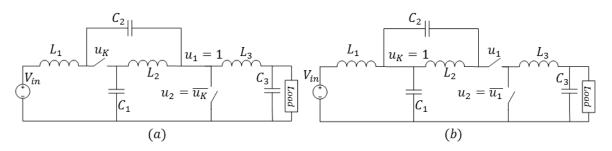

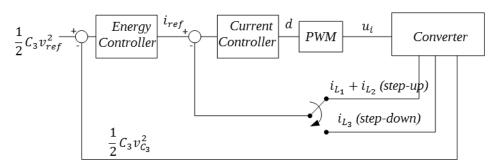

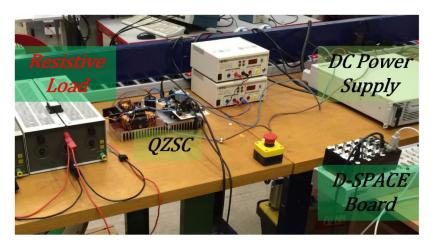

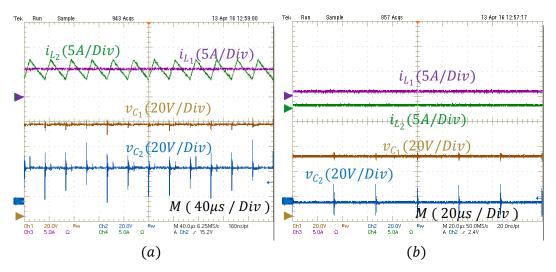

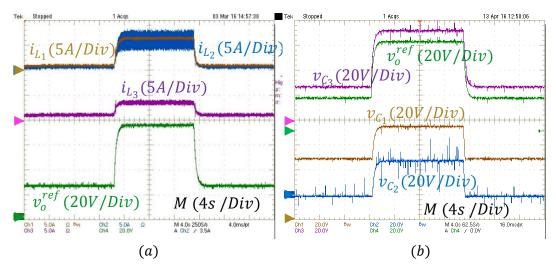

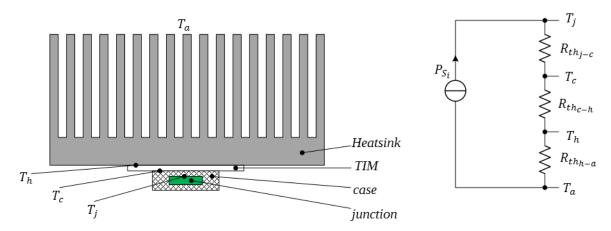

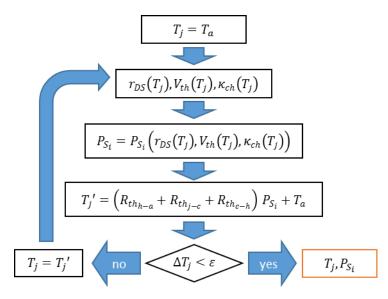

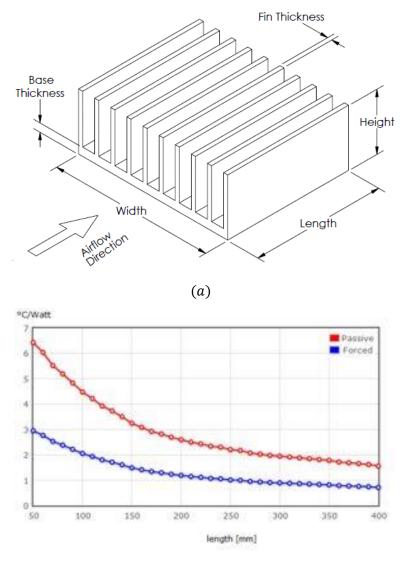

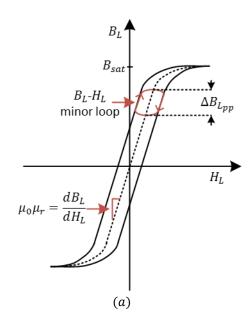

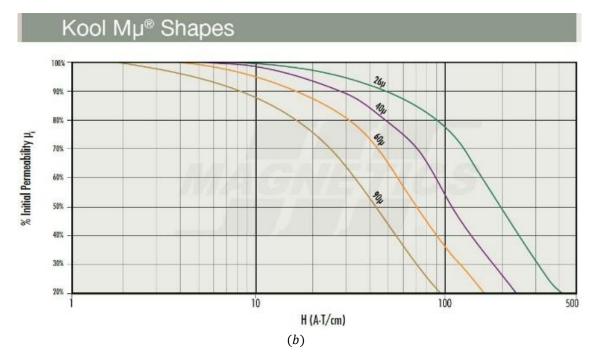

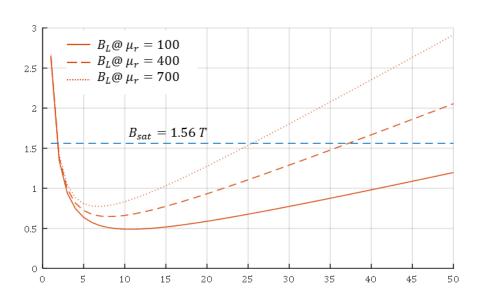

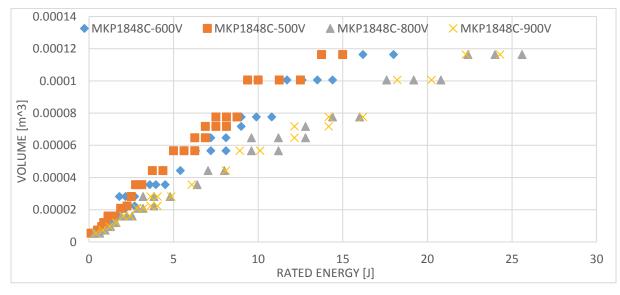

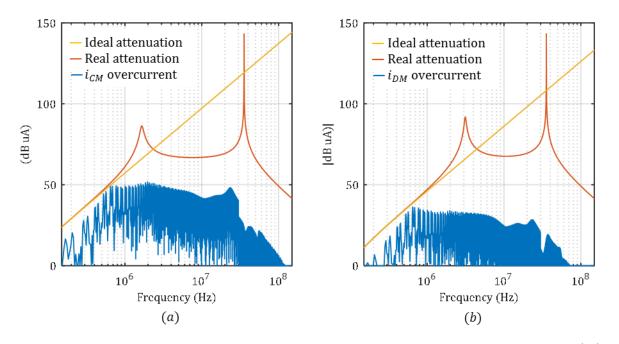

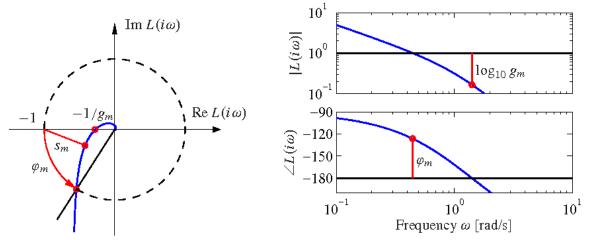

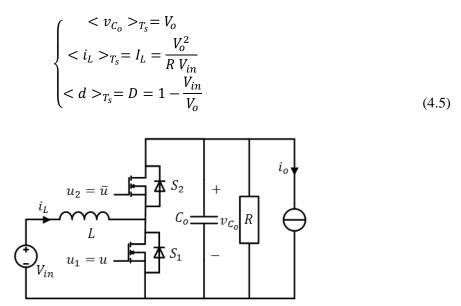

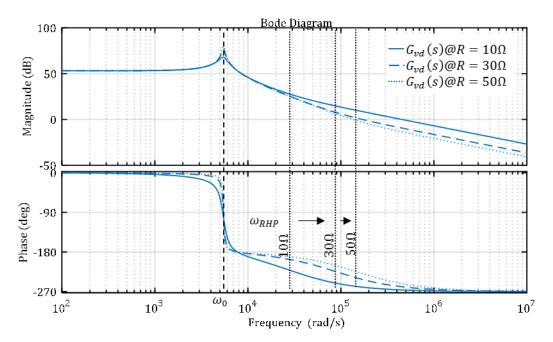

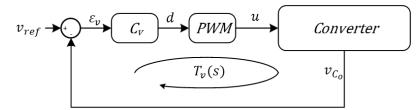

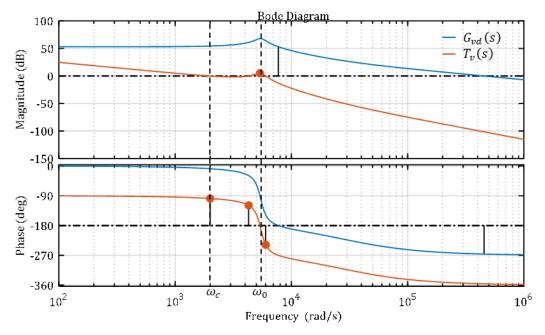

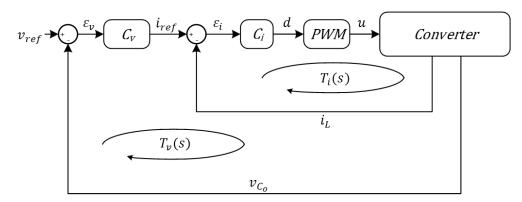

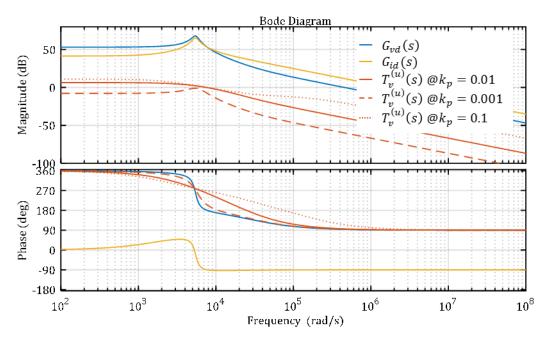

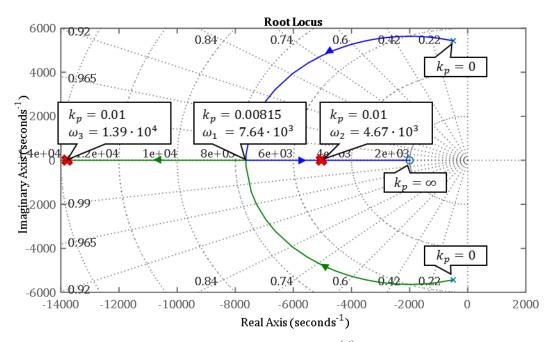

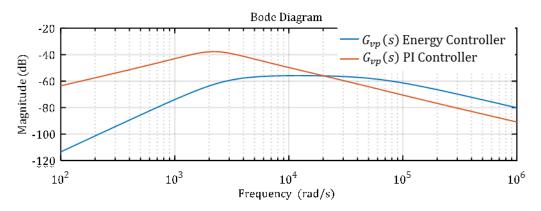

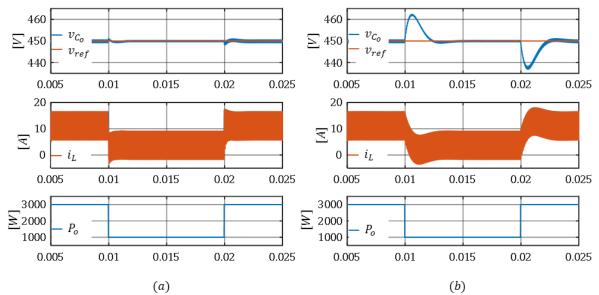

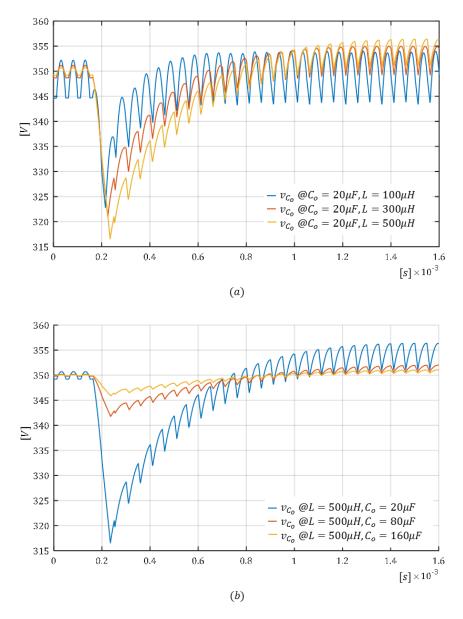

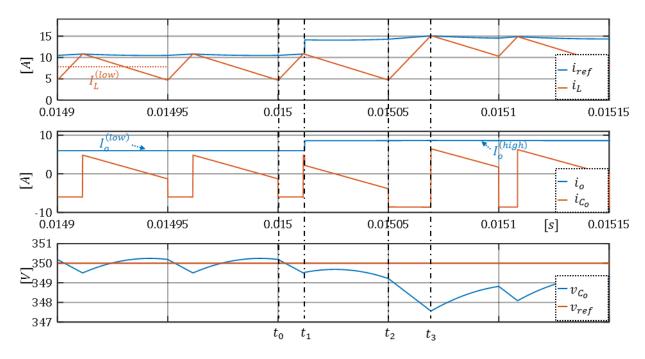

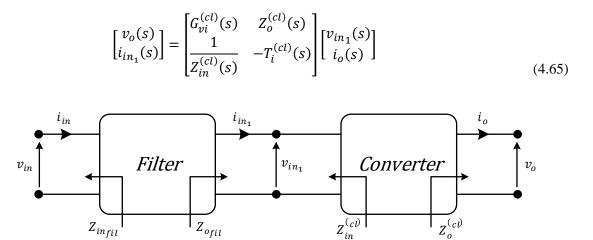

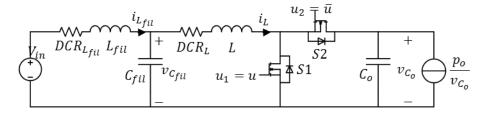

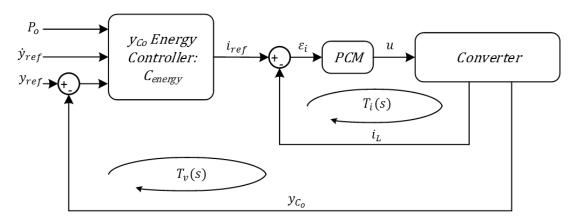

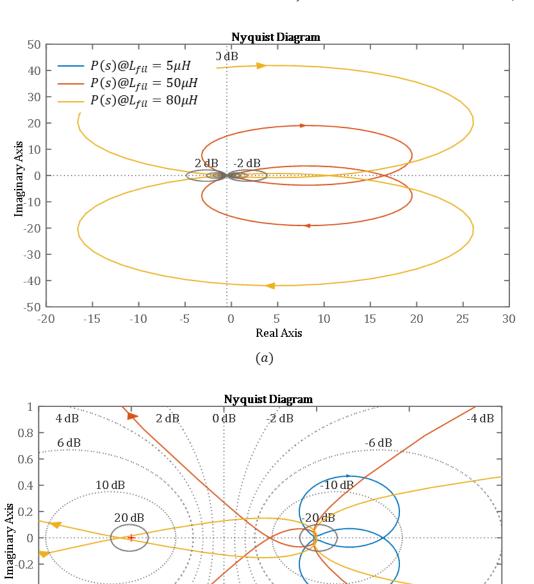

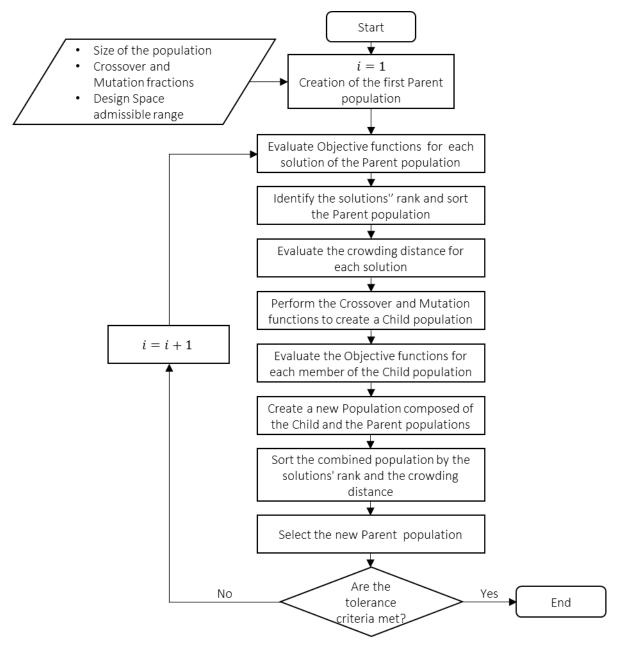

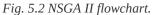

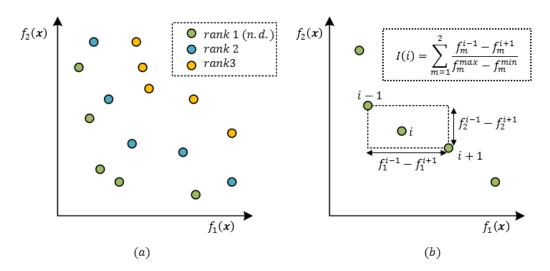

#### 1.3.2 Unipolar and bipolar technology: MOSFET and IGBT